初めてでも使えるVerilog HDL文法ガイド ―― 記述スタイル編

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月10日

3.テストベンチの基本

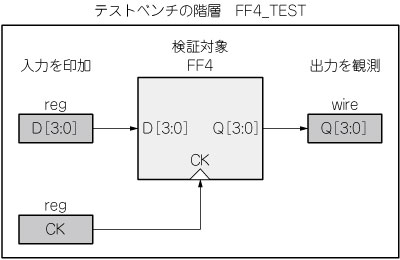

回路記述はシミュレーションにより検証します.このためには,検証対象となる回路に信号を与え,状態を観測するための記述が必要です.これがテストベンチです.設計した回路(モジュール)のファイル内にテストベンチを含めることも可能です.しかし,後々論理合成を用いてFPGAやASICに実装するので,図5のようにテストベンチは階層に分けて記述するのが一般的です.逆に言えば,テストベンチは論理合成対象外なので,Verilog HDLの記述力を最大限に利用できます.

図5 シミュレーション時のモジュール構造

検証対象の一つ上の階層でテストベンチを作成する.ここで入力を与えて出力を観測するしくみを作る.

リスト9に図4の4ビット・フリップフロップをテストするためのテストベンチを示します.記述のための必要事項を順を追って説明します.

リスト9 4ビット・フリップフロップのテストベンチ

1) ポートのないモジュール

この階層は最上位階層に位置するので,外部とやり取りするポートは不要です.ポートがありませんから,モジュール名の後はセミコロンで終わります.

2) 入力を用意する

検証対象回路に外部から信号を与えるため,変数宣言で信号を定義しておきます.リスト9では,FF4に与えるクロックとD入力を変数宣言しています.一方,出力はwireを使ってネット宣言しておきます.

また,1クロックの周期もパラメータ宣言を用いて定義しておきましょう.この場合,1ステップ1,000ユニットです.ユニットとは,シミュレーション時の時間の最小単位です.ユニットと実時間の対応は,コンパイラ指示子の`timescaleを使います(文法ガイド編を参照).

3) クロックを作成する

シミュレーション中つねにクロックを発生させるためには,alwaysを用いて記述します.#は遅延を意味します.

- CKを'0'にして半周期遅延

- CKを'1'にして半周期遅延

これを繰り返すことで,デューティ50%のクロックCKを作成できます.遅延量をくふうすれば,デューティを変えたり,多相クロックを作ることも可能です.

4) 検証対象を接続する

検証対象に入出力の信号を接続します.あらかじめ宣言しておいた変数やネットを接続します.複数のモジュールを接続することにより,複数ブロックの検証も可能です.

5) 入力を与える

initialを用いて入力を順次与えます.initialは,alwaysと対称的に,シミュレーション開始後に1回だけ実行します.プログラム言語に近い動作です.ただし,alwaysやinitialはいくつでも記述できますから,並列動作も可能です.

initialの中でD入力を変化させるたびに1周期の遅延を与えています.遅延を与えることでシミュレーションが進みます.最後にシステム・タスク$stopで停止します.

システム・タスクは$で始まり,表3~表5に示すようなものが用意されています.ファイル・アクセスが豊富にあるので,シミュレーション結果をすべてファイルに書き出すことや,よそで作成したデータとの自動比較も可能です.

表3 主要システム・タスク

表4 出力フォーマット指定

表5 ファイル入出力システム・タスク