初めてでも使えるVHDL文法ガイド ―― 記述スタイル編

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月27日

VHDLは,もともと米国防総省がハードウェア仕様記述言語として用意したもので,Verilog HDLに比べて「重い文法」になっています.ただし,論理合成可能な回路記述や,シミュレーションのための記述に限れば,それほど差はありません.概念上よく似た部分も多数あります.ここではVHDLの記述スタイルについて解説します.(編集部)

1. 基本構造

● VHDL記述の基本構造はentityとarchitecture

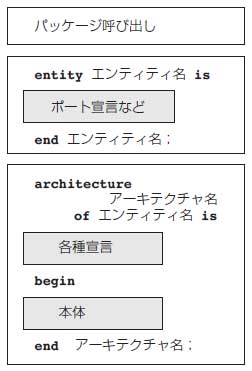

図1に示すように,VHDLの基本構造は,

- パッケージ呼び出し

- エンティティ(entity)

- アーキテクチャ(architecture)

からなります.この構造で,回路記述やシミュレーション記述を行います.

図1 VHDL記述のブロック構造

パッケージ呼び出しとは,各種演算子や関数などを定義した「パッケージ」を呼び出す部分です.実設計上,各ブロックの記述の先頭でかならず呼び出します.すべてのブロックに付き物と考えてください.記述上,とても重要な概念ですので,3節で詳しく説明します.

エンティティ(entity)は,外部とのインターフェースを記述した部分です.回路図で言えば「シンボル」に相当します.

一方アーキテクチャは,内部の動作を記述したもので,回路の本体です.回路図で言えば,「シンボル」に対応した内部の回路です.回路の構造や動作は,アーキテクチャ内で記述します.

以上の基本構造で,回路の記述やネットリストの記述,シミュレーション用の記述が可能です.

● エンティティは複数のアーキテクチャを持てる

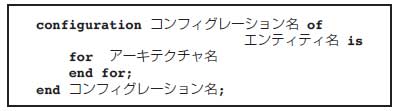

一つのエンティティは,複数のアーキテクチャを持つことができます.図2の例のように,一つのブロックでビヘイビア,RTL,ゲートの三つのアーキテクチャに対応することもできます.実行時にどれを選択するかは,コンフィグレーション宣言により対応づけられます.

|

図2 エンティティとアーキテクチャ |

● 基本構造の実例

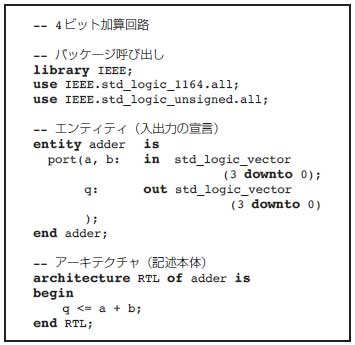

簡単な記述をもとに,基本構造の実際を説明します.リスト1は「4ビットの加算回路」です.二つの入力aとbの和をqに出力しています.

リスト1 加算回路記述例

(1) パッケージ呼び出し部

まずは「パッケージ呼び出し」です.ここでは,VHDL標準ライブラリIEEEの中の,std_logic_1164およびstd_logic_unsignedパッケージ内で定義してあるものすべてを読み込んでいます.型の宣言や,演算子を用いるために必要です.

(2) エンティティ

エンティティ内では,ポート宣言を行っています.

<ポート信号名>:<入出力の方向> <型>

の形式で宣言します.inとoutは予約語です.

<型>は,VHDLでは重要です.基本的に型が一致した信号どうしでのみ演算や接続が可能です.型が一致しないと文法エラーになります.ここでは,std_logic_vectorという型で,4ビットのポートを宣言しています.

downtoは,降順で範囲を指定する予約語です.昇順の場合toを使います.実際の設計ではもっぱら降順を使います.

(3) アーキテクチャ

回路の動作や構造はここで記述します.アーキテクチャ名は任意です.ブロックごとに変える必要はありません.筆者は,回路の記述ではRTL,シミュレーション記述ではSIMなどに固定しています.

回路の動作は加算演算子+と,代入文(この場合,アーキテクチャ直下に記述したので「同時処理代入」と呼ぶ)で記述しています.