初めてでも使えるVerilog HDL文法ガイド ―― 記述スタイル編

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月10日

2.RTL記述

RTLとは,意訳すれば「詳細なブロック図レベル」です.ANDゲートやORゲートを記述したりフリップフロップを並べるのではなく,セレクタやカウンタのレベルで記述します.これがRTLです.

RTLの記述には,以下の五つの記述スタイルがあります.

- assignによる組み合わせ回路

- functionによる組み合わせ回路

- alwaysによる組み合わせ回路

- alwaysによる順序回路

- 下位モジュール接続

2.1 assignによる組み合わせ回路

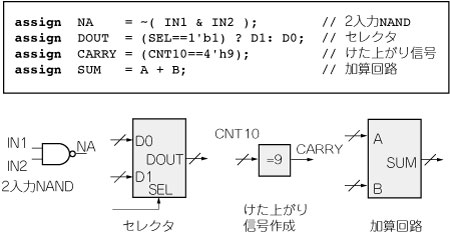

論理式1行で記述できる組み合わせ回路は,assignで記述できます.図2に例を示します.信号が1ビットか多ビットかは宣言で決まります.したがってセレクタや加算回路などの記述はビット数に影響されません.

図2 assignによる組み合わせ回路

assignだけでどこまで回路が書けるか挑戦しているような,assignだらけの記述を見たことがある.assignの多用は可読性が悪く,保守性が悪くなるのでご注意を.if~elseやcaseを使うとすっきり書けることが多い.

assignにより,AND,ORなどのゲート回路から,セレクタ,加算回路なども記述できます.関係演算子(==や<=など)は真のとき'1',偽のとき'0'となるので,図2のけた上がり信号(CARRY)のようなこともできます.また,ネット型の信号宣言と,この信号に対する代入を一度に記述することができます(リスト2).

リスト2 宣言と同時に回路を記述

各代入文は同時に実行されます.記述が前後しても動作に違いはありません.「代入」というより「接続」と考えたほうがわかりやすいでしょう.

2.2 functionによる組み合わせ回路

論理式1行で記述できないような組み合わせ回路,例えばデコーダやROMなどはfunctionを用いて記述します.ファンクション内では,if~elseや,caseなどの制御構造を使用できるので,複雑な組み合わせ回路を簡潔に記述できます.リスト3(a)にfunctionによる3 to 8デコーダの記述を示します.3ビット入力DINの値をデコードし,8ビット出力DOUTの中の1ビットだけが'1'となる回路です.

ファンクションは,予約語functionの後に戻り値のビット幅,ファンクション名,そしてファンクションの入力宣言と続きます.このファンクションの本体は,case文が一つだけです.入力DINに対して8通りに分岐し,一致した文を実行します.ファンクションの戻り値は,ファンクション名に直接代入することで行われます.case文,ファンクションはそれぞれendcase,endfunctionで終わります.

複数の文をまとめて一つの文として扱うときはbegin~endを使います.リスト3の例ではファンクション内はcase文しかありませんが,念のため付けておきました.文の末尾にはかならず;(セミコロン)を付けます.しかし,end~の予約語で終わっている場合は不要です.

ファンクションは定義側なので,呼び出し側が必要です.assignでファンクションDECを呼び出し,DOUTに代入してデコーダの記述は完了です.

2.3 alwaysによる組み合わせ回路

組み合わせ回路をalwaysで記述することも可能です.先ほどのデコード回路を,alwaysを用いて記述してみました(リスト3(b)).

alwaysによる組み合わせ回路の要点は,

- 出力をreg宣言する

- alwaysの@以降(イベント式ともいう)にすべての入力を記述する

- alwaysの中に動作(出力に対する代入文)を記述する

となります.

alwaysは「無限ループ」であり,@は「待ち」を作ります.@以降に記述された信号に変化があるときに,「待ち」が解除し,always内部を実行します.つまり,入力が変化すれば,出力に対する代入文を実行することになります.結局,組み合わせ回路になります.

リスト3(b)では@*と記述していますが,この * は,「入力信号のいずれか」を意味します.つまり,

@( 入力信号, 入力信号, 入力信号, ‥ )

とするところを省略して記述しています.多数の入力がある場合,簡潔に記述できます.

リスト3 3 to 8デコーダ