無償ツールで設計効率の向上を体験 ―― HDLコードの記述ルール・チェックを体験する

tag: 半導体 ディジタル・デザイン

技術解説 2009年6月16日

2.検査・修正機能の利用

ソース・コードによっては,警告がたくさんでることがあります.そのためALINTの設定を行うと便利になります.ALINTには,対象とするルールを選択したり,ルールによって分類して表示する機能があります.

(1)適用するルールの選択

メニューから「ALINT」→「ALINT Options」を選択し,適用する規則の設定を図5のALINT Optionsウィンドウで行います.

ALINT CommonタブのActive policy欄に「STARC_ALL」と入力します.警告が多いときは「STARC_TOP23」にします.設定可能なルールは表1の通りです.このほか,Configuration Managerを使うと,自由にルールを設定できます.

図5 適用するルールの指定

表1 用意されているルール

(2)ルールによる分類

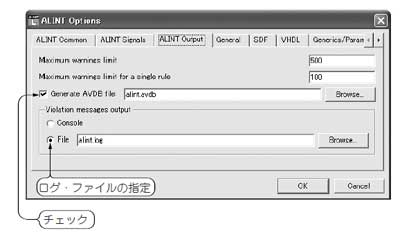

ALINT OptionsウィンドウのALINT Outputタブを選択し,ルールによる分類の指定を行います.

図6のように,Generate AVDB fileをチェックするとViolation Viewerを利用できるようになります.コンパイル時に拡張子が.advbというファイルが生成されます.advbファイルは,ソース・コードのファイル名と同じにしておくと便利です.Violation messages outputの「File」を選択するとログ・ファイルを保存します.

図6 ルールによる分類の指定

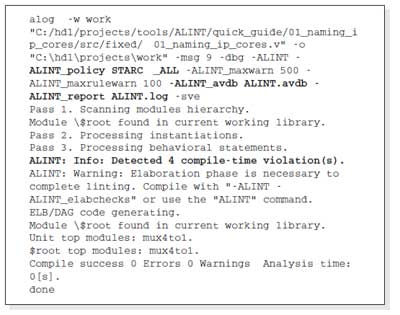

コンソール画面では,コマンドの実行と結果を確認できます.図7は,コンパイル・エラーはなく,ALINTの4種類の違反がある例です.

図7 コンソール画面の表示

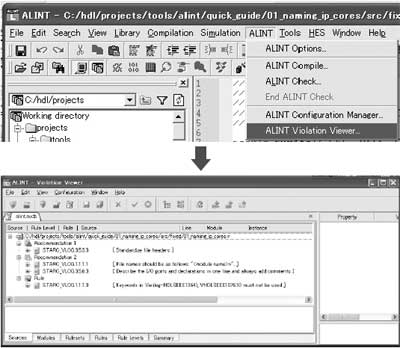

メニューから「ALINT」→「ALINT Violation Viewer」を選択し,advbファイルを読み込みます.

図8がViolation Viewerの画面です.画面の下のModulesやRulesetsなどのタブを選択すると,必須(Rule)や推奨(Recommendation)の区分ごとに表示したり,ファイルごとに表示したりします.違反するファイルの警告をダブルクリックすると,ファイルを開き該当する行を表示するので警告の分析と処理に役立ちます.

図8 ALINT Violation Viewer

図8では,Rule(必須),Recommendation1(推奨1),Recommendation2(推奨2)の3種類の分類の合計四つの規則に反していることが分かります.

- 推奨2の1.1.1の1番目の規則である「モジュール名とファイル名が同一である」に反している

- 3.5.6の3番目の規則である「可読性を高めるため宣言ごとに注釈(コメント)をつける」に反している

- 推奨1の3.5.3の3番目の規則である「ファイルの先頭の注釈の書式に従っていない」

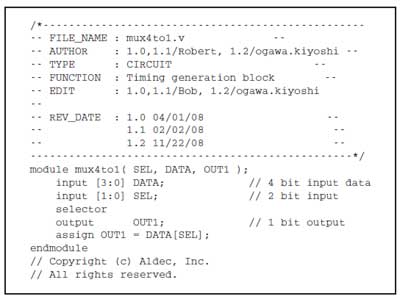

ファイルの先頭の注釈は,03_naming_bnf_headersのfixedフォルダの中に先頭の書式例があります.リスト2に修正したソース・コードの例を示します.

リスト2 修正したソース・コード

(3)複数のソース・コードを一括チェック

ここまでは画面に表示したファイルだけをコンパイルするCompileメニューを利用しました.ALINTメニューは,ソース・コードの検査だけを実行します.

複数のファイルのチェックを行いたい場合は,ALINTメニューを利用します.ALINTメニューを利用すると,ALINTコマンドを実行しています.

Quick Guideのソース・コードを実習すれば,ALINTで出る警告の半分くらいに対処できるようになるかもしれません.あるいは,最初から警告が出ないようなコードが書けるようになっているかもしれません.

ただし,すべての規則を守ることがよいとは限りません.規則を守らない方がよい場合には,MISRA-Cのように逸脱の手続きとして根拠を文書化するとよいでしょう(6).C言語におけるMISRA-Cでは,特定の場合には規則を守らない方が品質が高くなる場合があり,「逸脱の手続き」を取ることも規則になっています.

筆者ら(名古屋市工業研究所)は,2006年から中小企業の技術者向けのVerilog HDL研修を実施しています.6日間で36時間のコースです.FPGA評価ボードと開発環境を使い,Verilog HDLによる設計からオシロスコープを使った動作の確認までを行います.C言語の知識を持つエンジニアを対象とし,Verilog HDLで記述ができるようになることを目標の一つにしています.

RTL設計スタイルガイドは,2007年より利用しています.C言語プログラマにVerilog HDLで記述してもらうと,RTL設計スタイルガイドに反する記述をします.違反内容を調査することで,Verilog HDLのどういう理解が不十分かが分かり,何を学習すればよいかが特定できるようになります.

その結果,RTL設計スタイルガイドの項目を図Aのように分類しました.

<1>実習を実施する前に知っているとよいこと

<2>実習をしながら勉強するとよいこと

<3>理解が進んでから自習するとよいこと

<4>実習の範囲外 実習前に<1>を説明し,実習の過程で<2>を理解してもらい,時間のある人には<3>を自習してもらうようにしています.その際,RTL設計スタイルガイドのルールをチェックできるツールALINTを使っています.

|

第1章 基本設計制約 |

第2章 RTL記述テクニック |

第3章 RTL設計手法 |

第4章 検証のテクニック |

* <1>実習前, <2>実習中, <3>自習, <4>実習外

図A RTL設計スタイルガイドの目次と実習の順序