無償ツールで設計効率の向上を体験 ―― HDLコードの記述ルール・チェックを体験する

tag: 半導体 ディジタル・デザイン

技術解説 2009年6月16日

ソース・コードの記述にあいまいさがあると,論理合成時に期待通りの回路に合成されず,不具合の原因になることがある.ここでは,米国Aldec社の「ALINT(エーリント)」を使って,HDLソース・コードの記述スタイルのチェックを体験する. (編集部)

STARC(半導体理工学研究センター)は,日本の半導体メーカを中心にHDL(Hardware Description Language)で記述したコードであるIP(Intellectual Property)コアを相互に利用できるようにするため,RTL(Register Transfer Level)の設計指針を取りまとめた「RTL設計スタイルガイド」を発行しています.Verilog HDL編とVHDL編があり,それぞれ日本語版と英語版があります.日本語版のVerilog HDL編は第2版になっています.規則は必須,推奨1,推奨2,推奨3,参考の五つのレベルに分かれています.ALINTは,参考以外の規則に対応するHDLコード検査ソフトウェアです.RTL設計スタイルガイドのVerilog HDL編に対応しており,VHDL編への対応を予定しているそうです.

1.記述ルール・チェックの基本

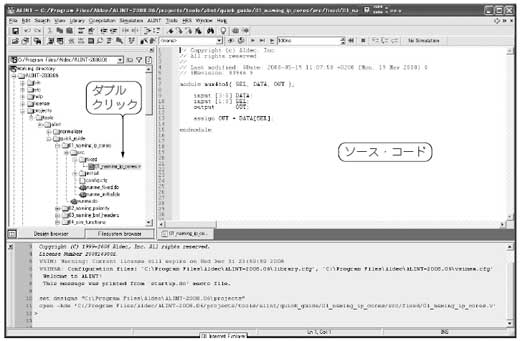

ALINTを起動すると図1の画面が開きます注1.メニュー,Design browser,ファイル編集,コンソール(コマンド入力・ログ表示)の四つの領域に分かれています.起動時に,Design browserには,ALINTをインストールしたフォルダを表示しています.

図1 ALINTの起動画面

注1: licence.datがlicenceフォルダにないか,ネットワーク・インターフェースが無効になっていると起動しない.

ALINTには,Verilog HDLを勉強するための12個の例題とクイック・ガイドが付属しています.今回は,この例題を使ってコードのルール・チェックを体験します.

(1)ソース・ファイルの読み込み

Design browserで,projects\tools\quick_guide\01_naming_ip_cores\src\fixedにある「01_naming_ip_cores.v」をダブルクリックします.図2のように,Verilog HDLのソース・コードがファイル編集画面に表示されます.

図2 ソース・ファイルの読み込み

(2)コンパイル

メニューから「Compile」→「Compile」を選択してコンパイルを実行します.

ライブラリの設定をしていないと,エラー(Compilation error)ダイアログが表示されるので,[YES]ボタンを押してライブラリを作成します.図3のライブラリ作成のウィンドウ(Create Library)では,Library and Mappingを選択し,Set as worklibをチェックします.Library Name欄が「work」になっていて,Library File欄が「work.lib」を含む指定になっていれば[OK]ボタンを押します.

図3 ライブラリの作成

コンパイルが始まります.一つのソース・ファイルを読み込むだけでコンパイルできるのは便利です.

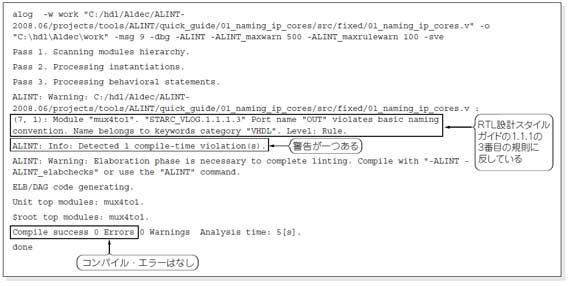

(3)コンパイル結果の確認

次に,コンパイル・エラーが出ていないかどうか,コンソール画面を確認します.

図4はコンソール(操作)画面の出力例です.「Compile success 0 Errors 」が,コンパイル・エラーがないことを示しています.「ALINT: Info: Detected 1 compile-time violation(s).」は,警告が一つあることを示しています.「(7, 1): Module "mux4to1". "STARC_VLOG.1.1.1.3" Port name "OUT" violates basic naming convention. Name belongs to keywords category "VHDL". Level: Rule.1.1.1.3」は,RTL設計スタイルガイドの1.1.1の3番目の規則に反していることを示しています.

図4 コンパイル時の操作画面(Console)

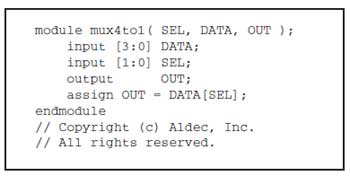

リスト1は,コンパイルしたソース・コードの本体です.OUTという変数はVHDLのキーワードです.そのままで使わないようにというのが今回の警告です.

リスト1 ソース・コード

(4)ソース・コードの修正

ファイル編集画面で,ソース・コード中のOUTをOUT1に変更します.再度コンパイルすると,警告がなくなることが分かります.

ここまでが一番簡単な操作手順です.ピン配置などの複雑な設定をしなくても,ルール・チェックができます.