CPLDはセンス・アンプ方式からCMOSへ ――米国Xilinx社が低電力CPLD「CoolRunner- II」を発売

米国Xilinx社は,消費電力の低いComplex PLD(CPLD)製品「CoolRunner-II」を発売する.同社は本製品を市場に投入することで,CPLD技術でつねに先行してきた米国Lattice Semiconductor社を追う立場から追われる立場になったと自信をのぞかせる.ここでは,Xilinx社 Vice President, Worldwide MarketingのSandeep Vji氏(写真1)にCoolRunner-IIの概要について聞いた.

[写真1] 米国Xilinx社 Vice President, Worldwide MarketingのSandeep Vji氏

――CoolRunner-IIの特徴は何ですか.

Sandeep Vji氏 CoolRunner-IIは,低消費電力が特徴である.当社(Xilinx社)がオランダのPhilips Semiconductor社から事業グループごと買い取ったZFP(Zero First Power)技術を採用している.ZFPとはCMOS技術を用いてCPLDの積項(プロダクト・ターム)を構成する技術である.製品ファミリとして,マクロセル数が32~512の6品種を用意している(表1).ピン間伝播遅延時間(tPD)は3.5ns~6.0ns.最大動作周波数は300MHzである.

[表1] CoolRunner-IIファミリ

| 型名 | XC2C32 | XC2C64 | XC2C128 | XC2C256 | XC2C384 | XC2C512 |

| I/Oのサポート | LVTTL, LVCMOS |

LVTTL, LVCMOS |

LVTTL, LVCMOS, SSTL, HSTL |

LVTTL, LVCMOS, SSTL, HSTL |

LVTTL, LVCMOS, SSTL, HSTL |

LVTTL, LVCMOS, SSTL, HSTL |

| 使用可能ゲート数 | 750 | 1,500 | 3,000 | 6,000 | 9,000 | 12,000 |

| 最大I/O数 | 32 | 64 | 100 | 184 | 240 | 270 |

| tPD(ns) | 3.5 | 4.0 | 4.5 | 5.0 | 5.5 | 6.0 |

| I/Oバンク数 | 1 | 1 | 2 | 2 | 4 | 4 |

注:tPDの値は予定(preliminary data).

――従来のセンス・アンプを利用する方法ではなく,CMOS技術を用いたのはなぜですか.

Sandeep Vji氏 従来のセンス・アンプを利用する方法では,一つのEPROMセルに二つのバイポーラ・トランジスタが使われている.二つのバイポーラ・トランジスタを駆動するために,合わせて1.4Vの電圧を供給する必要がある.電源電圧が1.8Vまで下がってくると電圧のマージンが少なくなり,性能を引き出すことが難しくなる.一般に,プロセス技術が微細になると電源電圧は下がる.従来のセンス・アンプ方式ではこのトレンドに対応していくことができない.一方,CMOS技術を用いると,このような問題は発生しない.継続的にプロセスを微細化することができる.CPLDをCMOS技術で製造することは,昔でもできた.しかし,2.5V以上のデバイスではセンス・アンプを用いた方が性能が良かった.

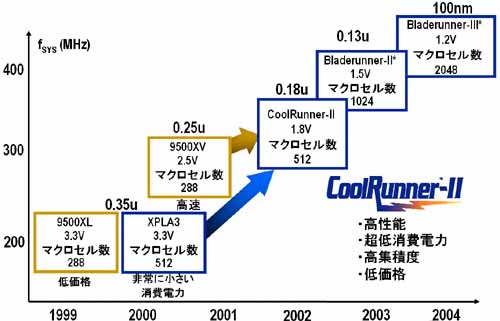

当社だけでなく業界全体の動向として,今後,CPLD製品はCMOS技術を採用する方向に移っていくと考えている(図1).

[図1] Xilinx社のCPLD製品のロードマップ

Bladerunner-II,Bladerunner-IIIは開発コード名.

――消費電力を下げるため,ほかにどのような工夫をしていますか.

Sandeep Vji氏 CoolRunner-IIのスタンバイ電流は100μA未満である.加えて,CoolCLOCK機能により,内部配線の消費電力を削減できる.CoolCLOCKとはクロック分周器とクロック・ダブラを組み合わせた機能である.たとえばクロックを2分周して入力した後,マクロセルの中で,必要に応じてクロックを2倍にする.性能を維持したまま,内部クロックを細かく制御できる.

――従来のXC9500ファミリはどうなりますか.

Sandeep Vji氏 XC9500ファミリの出荷は今後も続ける.ただし,製造プロセスをシュリンクさせた新製品の開発は行わない.

――2001年12月にLattice社がCOMS技術を使った低消費電力の製品(ispMACH4000)を発表しています.CoolRunner-IIとispMACH4000の違いを教えて下さい.

Sandeep Vji氏 Lattice社がCMOS技術の製品を市場に出荷するのは,今回が初めて.これに対してCoolRunner-IIは当社の第2世代の製品である.また,CoolRunner-IIの消費電流はLattice社の1/2,最大スタンバイ電流はLattice社の1/100である.さらに,CoolRunner-IIは,消費電流を下げるためのCoolCLOCK機能とパワー・マネージメント用のData Gate機能を持っているが,Lattice社の製品は持っていない.

――CoolRunner-IIとispMACH4000のほかに,CMOS技術を使ったCPLD製品を出荷している企業はありますか.

Sandeep Vji氏 米国Cypress Semiconductor社が高集積で高価格帯の製品を出荷しているようだ.しかし,市場セグメントが異なるので,今回の製品と競合するとは考えていない.

――プログラミング・データの保護について,どのような対策を取っていますか.

Sandeep Vji氏 あまり詳細を話すとセキュリティの意味がなくなってしまうので話せないが,デバイス中に読み出し不可能なビットをばらまいている.リバース・エンジニアリングができないようにした.あるゲーム・メーカに見せたところ,高く評価してもらった.無理やり中身を解読しようとすると,デバイス自体が内容を消去してしまうなどの対策を施している.

――CoolRunner-IIはどのような高速I/O規格をサポートしていますか.

Sandeep Vji氏 LVTTL,LVCMOS,SSTL,HSTLをサポートしている.たいていのCPLDの設計ではLVTTLとLVCMOSの規格が使われていると思う.今回から高速メモリに対応するため,SSTLとHSTLのサポートを始めた.

――出荷時期はいつですか.

Sandeep Vji氏 CoolRunner-IIファミリ製品の一つである「XC2C64(64マクロセル)」は現在出荷中である.そのほかの5種類の品種の出荷は,2002年後半に予定している.

ザイリンクス株式会社のホームページ

・http://www.xilinx.co.jp/