[ keyword: LSI ]

Lattice,電源電圧1.8V,静止時の消費電流1m~3mAのCPLDを発売

ニュース 2001年12月3日

米国Lattice Semiconductor社は,電源電圧1.8Vまたは2.5Vで動作し,静止時の消費電流が1m~3mAのCPLD「ispMACH4000」を発売する.ispMACH4000では,マクロセル数が32~512の6品種を用意する(表1).

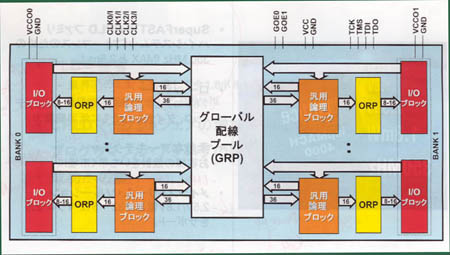

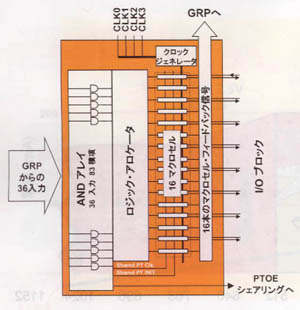

ispMACH4000は内部に独立して入出力電圧を規定できる二つのバンクを持ち,LVTTLや1.8/2.5/3.3VのLVCMOなど,異なった入出力レベルに対応できる(図1).また,論理ブロック一つ当たり36入力,80積項のANDアレイを備えている(図2).

ispMACH4000は,0.18μmルールのCMOSプロセスで製造する.これによりコア電圧を下げ,静止時,動作時両方の消費電流を抑えることができた.例えば,256個のマクロセルを搭載する品種(ispMACH4256)では,静止時の消費電流は2mAであり,動作周波数が100MHzのときの消費電流は30mA~35mAである.

また,伝播遅延時間も短縮された.積項数が5のときのピン間の伝播遅延時間は2.5ns,積項数が20では3ns,積項数が80では4ns~5nsである.動作周波数は,マクロセルが32個のときは最大350MHz,マクロセルが256個のときは最大300MHzである.

同社は,ispMACH4000向けの設計ツール「ispLEVER」も提供する.従来のCPLD製品に加え,今まで別ツールを用意する必要があったispGDX(スイッチLSI)も設計できる.既存の顧客には無償で提供する.600マクロセルまでの機能限定版については,同社のWebサイトで無償公開する.

同社は,顧客の要求に応じてアーキテクチャを最適化した「BFW(Big-Fast-Wide:高集積-高速-多入力)」製品を提供している.今回発表されたispMACH4000は,第3世代のBFW製品群におけるSuperFastファミリ(高速CPLD)の最初の製品となる.今後は高集積製品,多入力製品の出荷を予定している.

マクロセルが256個の「ispMACH4256」と512個の「ispMACH4512」はすでに発売を開始している.そのほかの製品は2002年上半期に発売をする予定.

[図1] ispMACH4000ブロック図

[図2] 汎用論理ブロック構成図

[表1] ispMACH4000ファミリの概要

マクロセル数

最大動作周波数

ピン間の伝播遅延時間

I/O数

パッケージ

48TQFP

48TQFP

100TQFP

128TQFP

176TQFP

256BGA

256BGA

256BGA

■価格 |

■連絡先 |