ハードウェア高位設計統合開発環境 「NSL Overture」

tag: 組み込み

2010年12月22日

NSL Overture

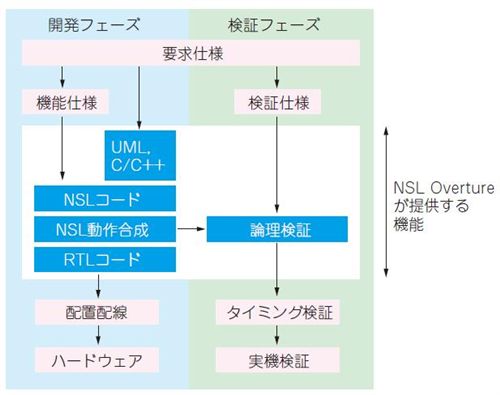

NSL Overtureとは,オーバートーン株式会社が提供する新世代のハードウェア記述言語NSL(Next SynthesisLanguage)の統合開発環境(図1)です.本製品は,NSL専用入力エディタや急速に普及が進んでいる統一モデリング言語UMLからNSL生成機能を持ち,中核となるNSL動作合成エンジンNSL Coreにより既存RTLコード出力します.また検証環境として論理シミュレータや,各FPGAメーカの開発ツールを起動することでFPGA のコンフィギュレーションデータの生成までを統合したEclipseベースの統合開発環境です.現在,組込みシステムや画像処理などの信号処理をC 言語にて開発しているエンジニアやRTL(Verilog HDL,VHDL)によるASIC/FPGA 開発のエンジニア,これからハードウェア設計を始めようと方々まで幅広くお使いいただける開発環境です.

図1 NSL Overture の開発フロー

NSLとは

年々増加する回路規模への対応のため新たに開発された新世代のハードウェア記述言語です.動作記述の抽象度が高く,クロックサイクルの制御が可能な言語で,Verilog HDL とVHDL の特徴を活かした言語仕様にC 言語を取り入れたため,少ない量で回路を記述することができます.また,既にVerilog HDL やVHDL にて開発したIPコアを取り込むことも特徴の一つです.

NSL Overtureの主な機能

NSL Core

オートビルド,RTL出力言語選択機能によりRTLコードを出力します.論理合成用として,Verilog HDLとVHDLをサポートし,検証用としてSystemCもサポートします.

NSL エディタ

予約語の色付けやコード補完だけでなく,ソース中で使われる信号名や変数名を一覧して表示させるアウトライン機能やデバッグ支援機能を有するテキスト入力エディタです.

UML to NSL( UML入力ツール)

UML によるハードウェア開発支援として,UML Profi lefor NSLを提唱し,クラス図から回路の上位階層となるNSLスケルトンを出力します.

NSL 検証ツール

ビヘイビア・シミュレータおよびVerilog論理シミュレータ(Icarus)と波形ビューワ(GTKWave)により検証をサポートします.また外部シミュレータ(ModelSim)の実行もサポートし,SytemCのシミュレータを利用することで,高速にかつC/C++のアルゴリズムとの検証も可能となり,相互で開発物の確認ができます.

ダイレクトインプリメンテーション

FPGAメーカが提供する開発ツールをNSL Overtureから直接起動し,FPGAのコンフィギュレーションデータを生成します.

![]()

オーバートーン(株)

営業部

〒160-0023

東京都新宿区西新宿8-15-2 西新宿タカノビル4F

TEL.03-6908-7923 FAX.03-6908-7924

E-mail:sales@overtone.co.jp

http://www.overtone.co.jp/