システムレベル設計と高位合成

tag: 組み込み

2010年12月21日

カメラの手振れ補正や画像認識などの複雑なアルゴリズムの設計の多くは,C/C++で開発され,このハードウェア化には多くの開発期間が掛かっています.そこで,システムレベル設計ツールを活用すれば,様々なアーキテクチャの探求や,ハードウェアとソフトウェアの協調検証,ソフトウェア開発の前倒し,などが可能となり,開発期間が短縮されます.さらに,高位合成によりシステムレベルで記述した,C/C++ やSystemC をRT レベルのハードウェア記述言語(HDL)に具体化し,論理合成によりFPGAへ実装できます.ここではシノプシス社のツールを例に,システムレベル設計からFPGAの実装までの流れを解説いたします.

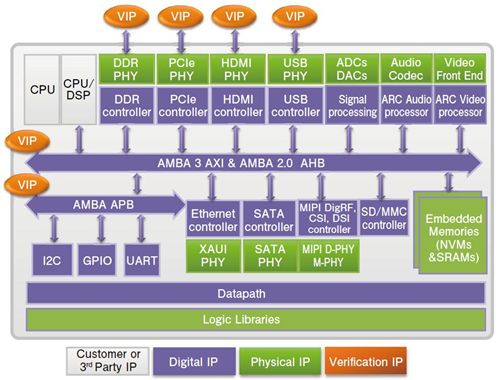

FPGA でシステムオンチップ(SoC)を実現できる時代がやってきました(1).図1に示すようにSoCは複数の部品(IP)で成り立っています.出来上がったI/O やメモリコントローラのIP は外部調達も比較的容易ですが,開発工数が一番掛かるのはコアIP と呼ばれる信号処理アルゴリズムの部分でしょう.

図1 SoCによく使われる知的財産(IP).CPUやDSPを動かすためのソフトウェアはこの図に表示されていませんが,開発コストの大半を占めています.シノプシスは色つきのブロックのIP やコアIP 開発支援ツールを提供しています.

今までの開発手法では,基板を製作して,オンチップのロジック・アナライザでハードウェアをデバッグし,インサーキット・エミュレータ(ICE)でソフトをデバッグしていました.バグが見つかったらFPGA を焼き直せばいいという考え方は普通だったと思います.しかし,SoCになりますと必要なリソースは軽く300万ゲートを超え,論理合成や配置配線だけでも24時間以上かかるでしょう.焼き直すのが1 ~ 2回くらいなら開発日程に大きな影響は及ぼさないかもしれませんが,何回もとなると大幅な遅れが発生する可能性が高くなります.システムレベル設計手法はこの課題を解決するものです.

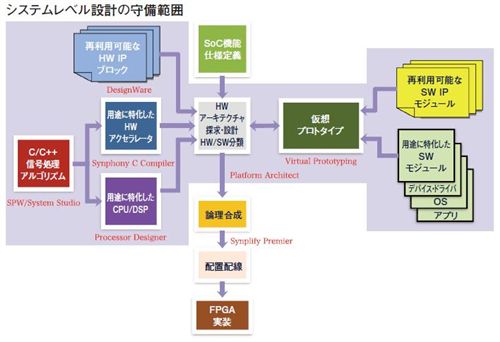

システムレベル設計は,アーキテクチャ探求,HW/SW分割,システム全体の最適化,ソフトウェア開発の前倒しを可能にするソリューションです(2).シノプシスが提供しているシステムレベル設計ソリューションは図2に示しています(3).システムレベル設計手法を採用することによって複雑なアルゴリズムの開発期間も大幅に収縮できます.

図2 FPGA に実装したSoC 開発の推薦フロー.ハードウェアが出来上がる前にソフトウェアを本格的にデバッグできるのはESL の一つの特徴です.配置配線はFPGA ベンダーのツールで実行します.

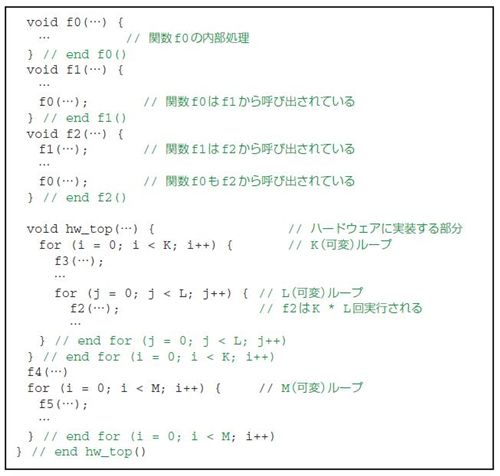

身近に使われているアルゴリズムの例を挙げてみますと,カメラでは,手振れ補正,スマイル認識,H.264の画像圧縮などがあり,携帯電話では,OFDM変復調,ターボ復号,MIMO 受信などがあります.アルゴリズムの良さを検証,証明するにはプログラムを書かなければなりません.複雑なアルゴリズムのプログラミングにはC/C++がよく使われています.C/C++では高い抽象レベルでアルゴリズム記述ができ,シミュレーション実行速度も非常に高速なため,最先端の開発研究機関で採用されています.C/C++プログラムは基本的に逐次的に記述されていて,時間の概念が無いため,その記述から自動的にハードウェアを合成するのは困難でした.C/C++ プログラムにはネステッド・ループや関数の中から別の関数を呼び出す記述がよく使われています.例えば,下記のような記述です.

高位合成が抱える課題の代表的なものには,

* 処理速度を上げるため,逐次的な記述からどのように並列処理を推測するか?

* タイミングを満足しつつ面積を最小化するため,どのようにリソース共有化を行うか?

といった問題があります.これらを同時に満たすのは不可能でトレードオフが必要です.上記のアルゴリズム例をハードウェアにする場合,次のようなアーキテクチャが考えられます.

* KとMのループに相互依存性がない場合,並列実行

* 関数f0はいくつかのところに呼び出されているため,タイミングが許す限り共有化

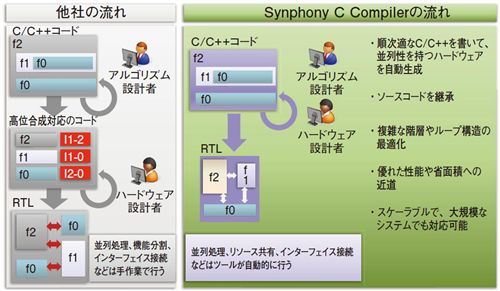

Synphony C Compiler(以後SCC)はシノプシスの高位合成ツールです.SCC はC/C++ の高い抽象度を維持したままで上記の課題をクリアできます.プログラムの流れを解析し,依存性のないループは自動的に並列にスケジューリングします.そして,図3に示すようにf0を「共有化可能」と指定すれば,SCCは必要な制御回路を自動生成し,タイミングを満たしながら可能な限りリソースを共有します.他の高位合成ソリューションはソースコードのレベルで時間の概念や並列処理の概念を導入するため,抽象度が落ちてしまい,コンパイル・実行するにはC/C++ 以外の環境が必要となってしまいます.

図3 Synphony C Compiler と他社の流れの比較.合成可能な形に持っていくには元のソースコードにかなり手を加えなければならないため,アルゴリズム設計者はコードが理解し難い状態になってしまいます.手作業でやらなければならないことが増え,バグが入り込む余地も増えてしまいます.

SCC はC/C++の高い抽象記述を維持したままでHW 化を実行できますので,さまざまな最適化を試みて,トレードオフを追及できるため300万ゲート相当のデザインに対応できます(4).SPWまたはSystem Studioを採用するとアルゴリズムのテストベンチを用意に構築できます.Platform Architectを使用して,アーキテクチャ探求,HW/SW分割が終了した時点で,仮想プロトタイプを構築してSW開発の前倒しを実現できます.HW をRTLに実装した後は,Synplify Premierを用いてターゲットのFPGA デバイスに合わせた更なる最適化とデバイスへのインプリメントを自動実行できます.FPGA でSoCを実現する際,前述のように,最適なシステムレベル設計手法を導入することによって開発期間の短縮,リスク削減,コストダウンなどの利点が得られます.

参考文献

(1)「ザイリンクス,ARM ベースのプロセッシング アーキテクチャを発表,エンベデッド システムにおいて比類ないレベルのパフォーマンスを実現」,ザイリンクスプレスリリース,2010年4月28 日. http://japan.xilinx.com/japan/j_prs_rls/2010/fpga/28nm-arm-architecture.htm

(2)「システムレベル設計概説」,福井正博,立命館大学理工学部電子情報デザイン学科,2004年7 月10 日.

http://www.ritsumei.ac.jp/se/re/fukuilab/outline/20040710_VLSI_System_design.pdf

(3)Synopsys System-Level Design.

http://www.synopsys.com/Systems/Pages/default.aspx

(4)「動画処理アルゴリズムの評価に高位合成を使ったら」,オリンパスの研究開発会社が講演,小島郁太郎,Tech-On!,2010年10月19 日.

http://techon.nikkeibp.co.jp/article/NEWS/20101019/186594/?P=2