Synphony C Compiler

tag: 組み込み

2010年12月22日

エレクトロニクス製品は,機能が複雑化する一方で製品ライフサイクルは短期化の一途をたどり,開発期間も短縮が求められています.今までの人海戦術の開発スタイルでは対応仕切れなかった課題ですが,現在では,エレクトロニック・システムレベル(ESL)設計支援ツールによって対処できるようになっています.ESL設計手法の採用によって開発早期段階(プロトタイプ基板が出来上がる前)に以下の点を実現できるためです.

*システム・アーキテキチャ設計

*機能実現手段をHW とSW に分割

*システム全体の最適化

*ソフトウェア開発の前倒し

*アルゴリズム的なコアIPのC/C++コードからRTL実装への自動化

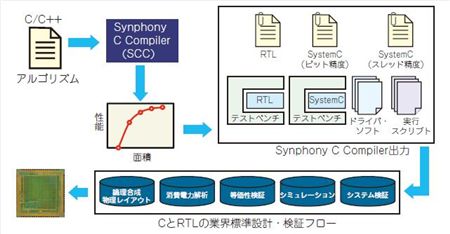

アルゴリズム的なコアIP とは製品の差別化のキーとなる機能ブロックのことです.大抵の場合,画像処理や通信機能を示しています.このような分野ではアルゴリズムが複雑で高速シミュレーション速度が必須のため,機能記述の抽象度が高いC/C++が良く使われていますが,RTL へのインプリメンテーション・パスが必要になります.300万ゲート以上になるシングル・スレッド記述のC/C++から高いQoR(結果品質)を持つマルチ・スレッドのRTL を自動合成するツール,Synphony C Compiler(以後SCC)をご紹介します(図1).

図1.Synphony C Compilerの設計フロー

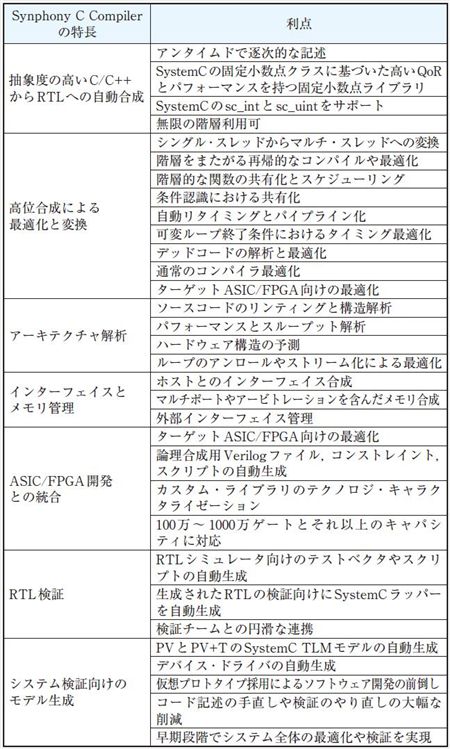

SCCは抽象度の高いC/C++ 記述からプログラムの関連性や依存性の自動分析を行い,実装ターゲットのASIC/FPGA 向けに最適されたRTL を自動生成する高位合成ツールです.SCC の特長は以下(表1)の通りです.

表1 Synphony C Compiler の特長と利点

Synphony C Compilerはアルゴリズム的なコアIPのアルゴリズム開発からRTL実装への近道です.

![]()

日本シノプシス合同会社

フィールド・マーケティング・グループ

〒140-0014 東京都品川区大井1丁目28 番地1 号

住友不動産大井町駅前ビル8階

TEL.03-5746-1500 FAX.03-5746-1550

E-mail:mkg_info@synopsys.co.jp

http://www.synopsys.co.jp/index.html