インテグリティな技術コラム(9) ―― メモリ・モジュールのクロック分配

●ICの数が増えた場合はクロック・アンプを利用

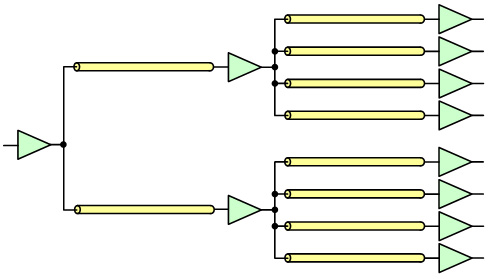

クロックは波形乱れとスキューに対する要求が厳しいため,ボード設計の際には一般信号よりも優先して配線します.以前は,1対1または1対nでクロックを分配し,さらに多くのICにクロックを供給する場合は,いったんクロック・バッファまたはクロック・アンプと称するICでクロックを受けて,さらに1対1または1対nで分配を続けました.例えば図4に示すように,1対2と1対4を組み合わせて,8個の負荷にクロックを分配します.

図4 1対2と1対4を組み合わせたクロック分配

この方式は,基本的な1対1伝送,またはその変形の繰り返し回路なので,波形乱れはほとんど生じません.ただし,複数のクロック・バッファを経由するため,遅延時間のばらつき,すなわちスキューが生じます.このため,スキューを調整する回路を挿入したり,遅延時間を選別したクロック・アンプを用いたりしていました.

●高速化・高密度化に対応するためにクロック・アンプを省略

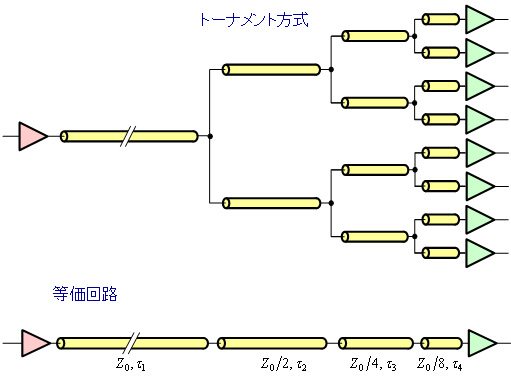

回路の高速化が進むと,もはやクロック・アンプ間の遅延時間のばらつきが無視出来なくなってきました.また,装置の軽薄短小化が進み,クロック・アンプを用いるスペース上の余裕がなくなってきました.このため,従来のクロック・アンプを省略して,直接接続するようになりました.例えば図5(a)のような接続形態です.最終の負荷からみるとトーナメントの形をしているので,「トーナメント方式」と呼ばれます.

図5 メモリ・モジュールのクロック信号

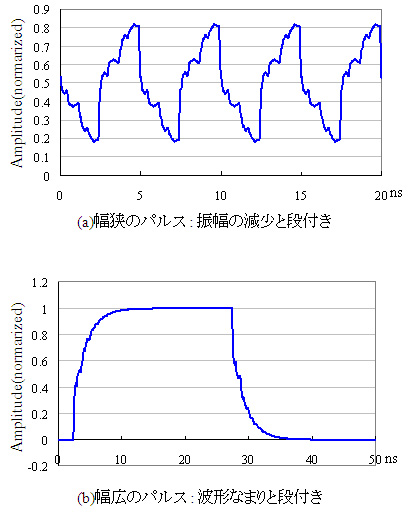

例えばトーナメント方式の1対8の分配において,線路のインピーダンスがZ0ですべて等しい場合,図5(b)のような等価回路に書き直せます.この場合,接続点がドライバとレシーバを加えて,5カ所も存在します.レシーバ端の波形は図6(a)のようになり,クロック波形の品質は,何とか「だましだまし」使うようなレベルというより,かなり危険な状態になっています.このような場合の波形品質は,実使用の周波数だけではなく,広いパルス幅で確認しておく必要があります.

図6 トーナメント方式のクロック波形

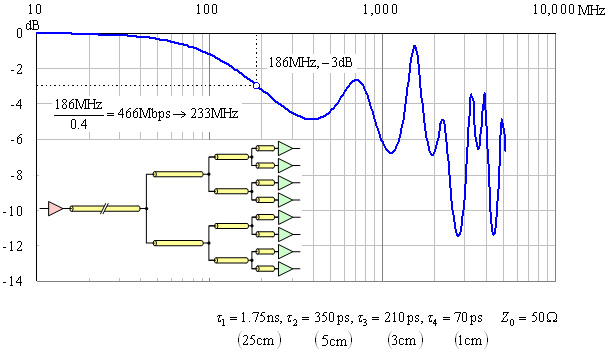

図6(b)は,十分に広いパルス幅の場合の波形です.実使用の周波数ではよく分からなかった波形の段が明確になります.この状態できれいな波形にしておく必要があります.図7は,この系を,前回と同じく周波数軸で眺めた場合の特性です.-3dBにおける周波数帯域は186MHzであり,せいぜいPC2-1000程度が限界と考えられます.

図7 トーナメント方式のクロック系の周波数特性

このようにIC内部ではクロック・アンプを介さない方式がごく普通に用いられていますが,IC内部は通常は抵抗とキャパシタによる等価回路で表される線路です.従って,RCの時定数による遅延を考えればよいので,波形割れの心配はあまりありません.一方,ボード上の配線は分布定数回路なので,インピーダンスの非整合に起因する波形乱れによる波形の段や割れに着目する必要があります.