DDRメモリの製品動向と基板設計のポイントを解説 ―― テクトロニクス・イノベーション・フォーラム2010

グラフィックス分野では顧客が2社だけ,という状況だという.企業名は明言しなかったが,パソコン用グラフィックス・ボードの大手ベンダである米国Advanced Micro Devices社(旧ATI Technologies社)と米国NVIDIA社のことだとみられる.データ転送速度が4Gビット/sのGDDR5 DRAMが主流で,5Gビット/sのものが認定作業に入っているとする.2011年には6Gビット/sに移行すると予測していた.

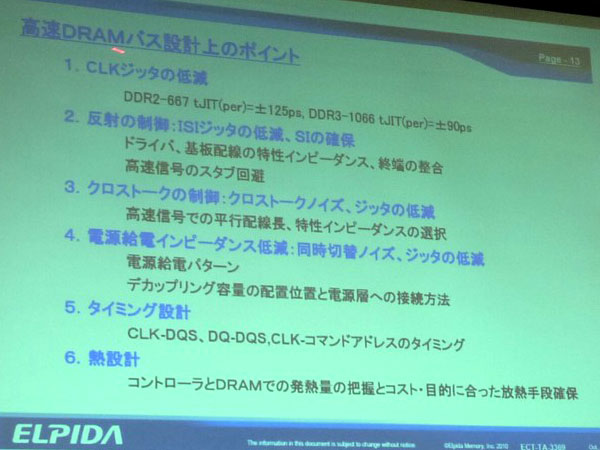

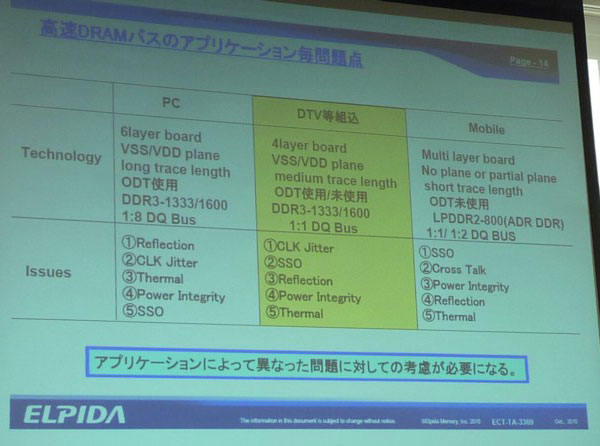

DRAMバスの基板設計を応用分野別にみると,パソコン向けが最も堅実であり,高速化が容易だという(写真5,写真6).プリント基板は6層と多めの配線層数が標準であること,オンチップ終端(ODT:On-die Termination)を使用していることなどがその理由である.これに対し,4層基板が標準のディジタル家電やオンチップ終端を嫌うモバイルなどでは,高速化が難しくなる.また高速化に伴う技術課題は,応用分野ごとに違う.パソコン向けは信号反射,クロック・ジッタ,放熱などが課題であり,ディジタル家電向けはクロック・ジッタ,同時スイッチング・ノイズ,信号反射などが課題であり,モバイル向けは同時スイッチング・ノイズ,クロストーク・ノイズ,供給電源品質などが課題だとしていた.

写真5 高速DRAMを実装したバスの設計要件

写真6 応用分野別にみた高速DRAMバスの設計課題

●DDRメモリ実装基板の信号品質と給電品質を解析

続いて紹介するのは,トッパン NEC サーキット ソリューションズの金子 俊之氏による「DDR3メモリの基板設計とシミュレーション事例」と題した講演である.DDRメモリなどの高速信号を伝送する基板の設計における,信号品質(シグナル・インテグリティ)と給電品質(パワー・インテグリティ)の解析手法を解説した.

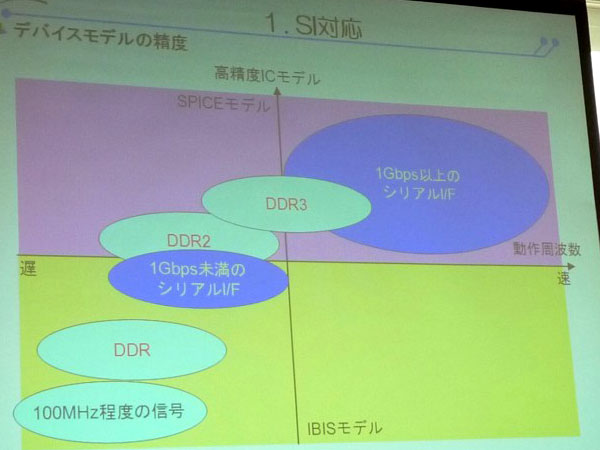

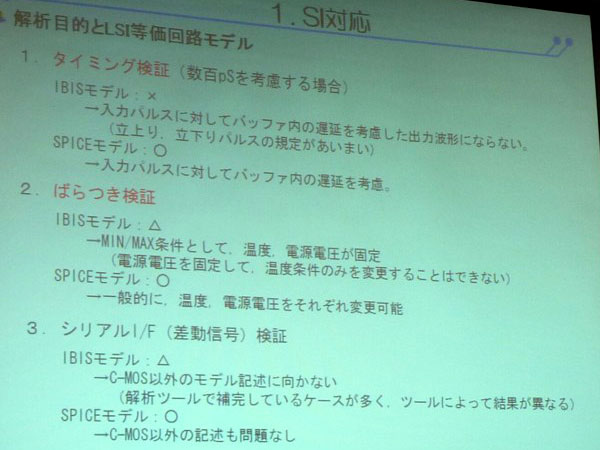

シグナル・インテグリティ解析では,データ転送速度が1Gビット/sを超える高速伝送基板では,半導体デバイスのモデルとしてIBIS(Input/Output Buffer Information Specification)ではなく,SPICEを使うべきだと主張していた(写真7).最も大きな理由はタイミング検証における精度の違いで,IBISモデルでは入力パルスに対するバッファ遅延を考慮していないので,数百ps(ピコ秒)といったタイミングの検証には不適切だとする(写真8).

写真7 データ転送速度とデバイス・モデルの関係

写真8 シグナル・インテグリティ解析における回路モデルの比較

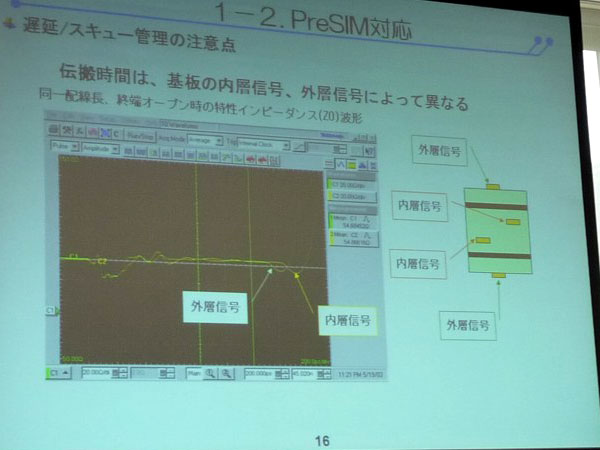

遅延およびスキューの管理では,外層の信号配線と内層の信号配線について配線長当たりの伝搬遅延時間が異なることに注意するべきだ,との指摘があった(写真9).差動信号配線で外層配線と内層配線を組み合わせることがあるが,等長配線だと伝搬遅延時間が一致しない.外層配線の周囲は大気であるため,比誘電率が低く,内層配線に比べると伝搬遅延が短くなるからだ.またDDRメモリ・コントローラLSIのパッケージが巨大化しているため,パッケージにおける遅延時間が無視できなくなっているという.

写真9 遅延およびスキューの管理における注意事項

パワー・インテグリティ解析では,電源インピーダンス(DDRメモリ・コントローラLSIの電源ピンと接地ピンの間のインピーダンス)の周波数特性を解析した結果から,外付けコンデンサの影響を具体的に示して見せていた.電源インピーダンスの解析にはプリント基板の配線容量だけでなく,チップ(シリコン・ダイ)とパッケージの容量も考慮すべきだとする.

Post a Comment