マイコン&FPGA開発の流れと開発ツール ―― 組み込みシステム開発の基礎知識(後編)

tag: 組み込み 半導体 ディジタル・デザイン

技術解説 2010年4月26日

● 機能設計

システム仕様書に基づいて,FPGAに実装する機能を「どのように処理するか」を検討します.また,ブロック図,外部インターフェース,ブロック間インターフェースなどの仕様を機能仕様書としてまとめます.

FPGAが持つ乗算器やメモリなどの機能や性能の確認をする必要がある場合には,FPGA開発ツールを使用します.

●論理設計

機能仕様書に基づいて,各ブロックのアーキテクチャを検討します.ブロック図,入出力,タイミング,状態遷移などの仕様を設計仕様書としてまとめます.FPGAの制約により,機能仕様を満たすことができなければ機能設計を再検討します.

●設計入力

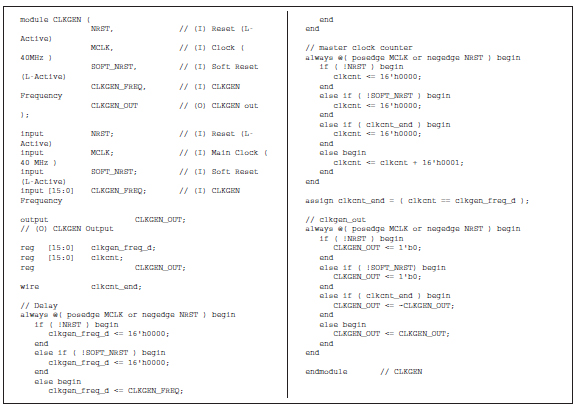

設計仕様書に基づいて,Verilog HDLやVHDLといった業界標準のハードウェア記述言語で論理を記述します(リスト5).開発ツールの回路図エディタにより論理回路図を入力したり,FPGA開発ツールが持つ独自の言語を使うこともあります.

リスト5 ハードウェア記述言語による論理の記述例(*クリックすると拡大します)

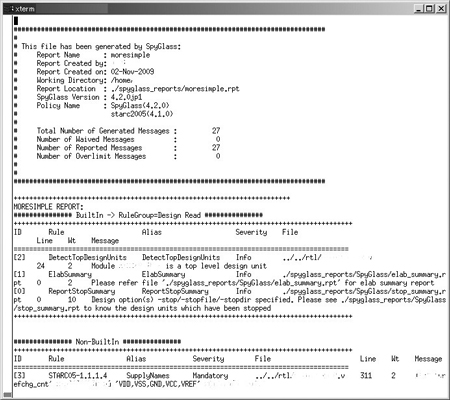

論理記述には,後工程の論理合成で期待通りの論理回路を生成するための記述ルールがあります.ルールに則った論理記述かどうかを確認するツールとしてAtrenta社の「SpyGlass」やSynopsys社の「Leda」などの文法チェッカがあります(図17).また,FPGA開発ツールでマクロやメモリなどを生成し,論理回路図や論理記述に使用します.

図17 文法チェッカの例

Atrenta社の「SpyGlass」とSynopsys社の「Leda」の画面を示す.

最近ではCベースの言語で機能を記述し,システム設計あるいは機能設計の段階でシミュレーションにより動作を確認するという手法も行われるようになってきました.機能記述から論理回路を生成するCadence Design Systems社の「C-to-Silicon Compiler」やMentor Graphics社の「Catapult」などの高位合成ツールなども出てきています.FPGA開発ツールの中には高位合成をサポートしているものもあります.この手法はプログラミング言語であるCやC++がベースになっているため,専用のシミュレータが不要という特徴も持っています.

●論理シミュレーション

設計した論理回路(または記述)を,機器上のFPGAで動かす前に,シミュレータを使用してコンピュータ上で論理動作を確認します.

機能をどのように確認するか書かれた資料をテスト仕様書といいます.シミュレーションにあたって,テスト仕様書に基づいて,論理回路とは別に外部端子への入力パターンを作成し,出力の観測点や期待値を指定します.これらをまとめてテスト・ベクタと呼びます.

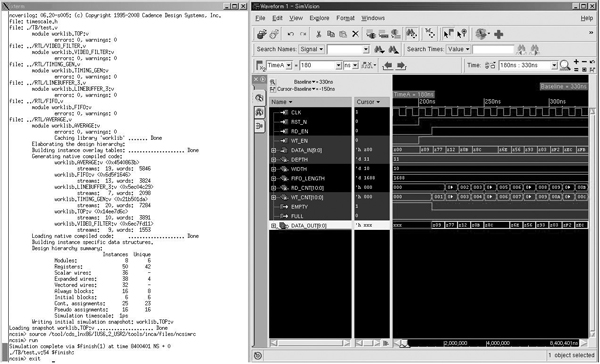

シミュレータで論理回路(または記述)とテスト・ベクタを読み込み,シミュレーションを実行します.

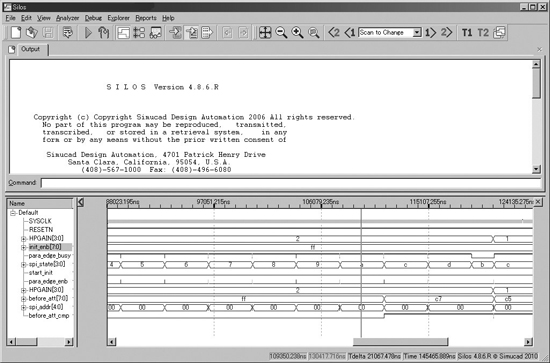

シミュレータには,ワークステーション上で動作するLSI設計用の非常に高価なものから,パソコン上で動作する安価なものまでさまざまです.前者には例えば,Cadence Design Systems社の「Incisive」やSynopsys社の「VCS」があります.後者としては,Mentor Graphics社の「ModelSim」やSIMUCAD Design Automation社の「SILOS」,Aldec社の「Active-HDL」などがあります(図18).また,FPGA開発ツールの中には簡易的なシミュレータ機能を持ったものもあります.

図18 シミュレータの例

Cadence Design Systems社の「Incisive」とSIMUCAD Design Automation社の「SILOS」の画面を示す.

「FPGAは何度でも書き直せるから論理回路ができたらとりあえず機器に入れて確認してみよう」という発想は,小規模回路であれば(力技を駆使して)成り立つかもしれませんが,大規模回路ではとても危険です.バグが内在するであろう複数のブロックが,FPGAの中で一斉に不具合を伴う動作を始めたらとても手には負えません.

LSI設計の世界では,LSIが出来上がってくるまで本当の意味での動作確認はできません.もし出来上がったLSIに不具合があれば,数千万円~数億円といった開発費が水の泡と消えます.ですので,シミュレーション(検証)を設計工数の何倍もかけてトコトンやります.

FPGAは現場で書き直せる特徴があるので,LSI設計ほどのシミュレーションは必要ないかもしれませんが,少なくともブロックは詳細に,全体は一通り動作するところまではシミュレーションで確認し,シミュレーションでは確認しづらい長時間動作などを機器上で確認するといった発想が必要です.

●インプリメンテーション

インプリメンテーションのほとんどはFPGA開発ツール上で処理できます.

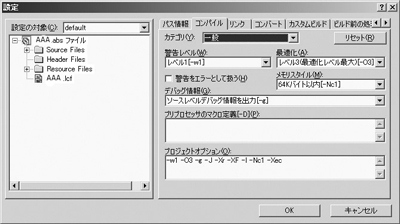

(1)環境(プロジェクト)構築

FPGA開発ツールの中で,使用するFPGAのファミリ/シリーズ名や具体的な型番,スピード・グレード情報や,コンフィグレーション方法,論理回路端子とI/Oピンの割り当てや動作周波数などのタイミング制約 などを,プロジェクトとして設定/管理します.

(2)論理合成

FPGA開発ツールの中で,論理記述(RTL)から論理回路を生成します.回路図エディタで作成した論理回路図には論理合成は必要ありません.

論理合成では,動作速度を重視するか,回路規模を重視するかなどの多くの合成パラメータがあります.一般的にはデフォルト設定から始めて,必要に応じてパラメータを設定していきます.

FPGA向けの論理合成ツールとしては,FPGAベンダが提供するツールのほかに,Mentor Graphincs社の「Precision Synthesis」やSynopsys社の「Synplify」があります.これらのツールは,より高い性能や,より小さい規模の回路を合成できるほか,FPGAベンダに依存せずに利用できることを特徴としています.FPGAベンダの開発ツールでも,このような外部論理合成ツールの出力を取り込む仕組みが用意されています.

(3)配置配線

FPGA開発ツールの中で,合成された回路をFPGA内部の基本論理ブロックに割り当て,各論理ブロック間の配線を選択し,FPGAに書き込む回路情報(コンフィグレーション・データ)を作成します.FPGA内部のどのあたりにどの回路を配置するかや,動作を確認した回路は再配置時に位置を固定するなどの設定パラメータがあります.一般的にはデフォルト設定から始めて,必要に応じてパラメータを変更していきます.

●タイミング解析

FPGA開発ツールの中で,配置配線された論理回路間の配線遅延や動作周波数などのレポートを確認します.必要に応じてインプリメンテーションに戻り,タイミング制約をかけますが,改善に限界があれば論理設計に戻りアーキテクチャを見直す場合もあります.

●タイミング・シミュレーション

FPGA開発ツールから,配置配線後の遅延情報が付加された回路情報(ネットリスト)を出力し,このネットリストとテスト・ベクタを使ったシミュレーションを行います.遅延のある,実機に近い動作を検証できます.

タイミング・シミュレーションでは,論理シミュレーションと同じシミュレータを使います.ただし,タイミング・シミュレーションには論理シミュレーションの何倍もの実行時間が必要です.LSI設計では必須ですが,FPGA設計の場合はFPGA内部で何が起きているか推測不能な場合などに行うのが効果的です.

●実機動作確認

パソコンとターゲット機器を専用ケーブルで接続し,FPGA開発ツールの書き込み機能を使って,機器上のコンフィグレーションROMにコンフィグレーション・データを書き込みます.FPGAに直接書き込むことも可能です.電源を再投入しコンフィグレーションが正常に終了すれば,機器上のFPGAの動作を確認するフェーズに入ります.

●参考・引用*文献

(1) * 山際伸一;ソフトウェアの開発環境を知る,マイコン超入門,ディジタル・デザイン・テクノロジ No.3,2009年10月.

うちざ・ひろふみ,おおいけ・ひろやす

三栄ハイテックス(株)技術本部

http://www.sanei-hy.co.jp/