IPコアで"ラクラク"FPGA設計 <Altera編> ―― SOPC Builderを活用した基本I/O&SDRAM制御回路の設計

tag: 半導体 ディジタル・デザイン

技術解説 2010年4月23日

3.回路の生成と動作確認

●アドレス配置と割り込み番号の自動割り当て

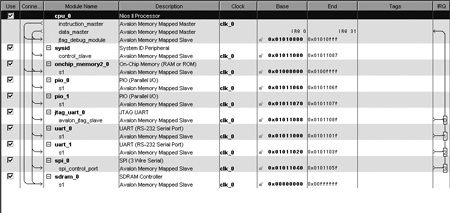

プロセッサ・コアにメモリ・コントローラやシリアル・コントローラなどを接続しました.次に,SOPC Builderで構成した機能ブロックにプロセッサから見たアドレス番地と割り込み番号を割り当てます.

SOPC Builderの右側の画面で,各々の機能ブロックのBase欄に先頭アドレス番地を,IRQ欄に割り込み番号を設定します.

この操作を手入力で行うと,ミスが発生する可能性があります.そこで,SOPC Builderでは自動的にこれらの値を割り振るコマンドが用意されています.

SOPC Builderの「System」メニュー内に,以下の二つのコマンドが用意されています.アドレスの設定は「Auto-Assign Base Addresses...」,割り込み番号の設定は「Auto-Assign IRQs...」を選択します.この操作により,自動的に効率的なアドレス配置を決め,割り込み番号を設定してくれます.

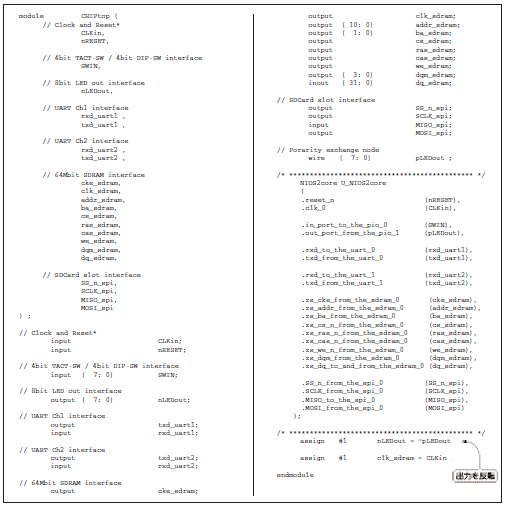

最終的に構成されたNIOS2core回路の構成を図13に示します.

図13 NIOS2core回路の構成(*クリックすると拡大します)

●HDLコードの生成

SOPC Builderで構成したシステムは,IPコア間の接続をしていただけで,実際に回路ができているわけではありません.そこで,[Generate]ボタンを押してHDLコードを生成します.HDLコードの生成には時間がかかりますが,成功すると,

Info : System generation was successful.

Info : No errors or warnings.

と表示されます.もしエラーが表示された場合は,設定に誤りがある可能性があります.モジュールの名称を確認し,いったん削除します.改めて正しく設定したコアを追加して再度[Generate]を行います.

SOPC Builderで生成されたHDLコードは,ほかのHDLコードと同じように利用できます.

生成されたコードは,SOPC Builderを起動したときに付けた名前になっています.今回の例では以下の2種類のVerilog HDLコードがプロジェクト・フォルダ内に書き込まれています.

- NIOScpu.v : Nios IIコア,PIO,JTAG-UARTなどを含む回路のVerilog HDLソース・コード

- NIOScpu_inst.v:ほかの階層からNIOScpu.vを呼び出すためのモジュール接続のひな型

ほかのコードから使用する場合には,下位階層にSOPC Builderから生成されたコードを位置づけます.ソース・コードの例をリスト1に示します.今回使用したFPGAボード上のLEDは,ボードの回路構成の仕様上,点灯方式が負論理になっています.つまり,ソフトウェアからは「0xFF」で全消灯,「0x00」で全点灯となります.そこで,PIO出力と,実際のFPGAの出力ピンの間に反転(NOT)記述を挿入しています.