IPコアで"ラクラク"FPGA設計 <Altera編> ―― SOPC Builderを活用した基本I/O&SDRAM制御回路の設計

tag: 半導体 ディジタル・デザイン

技術解説 2010年4月23日

2.基本I/O回路の設計

FPGAに接続されたSDRAMやLED,スイッチ,シリアル・ポートを使うための回路を作ります.

●スイッチ入力やLED表示のためのコアを設定

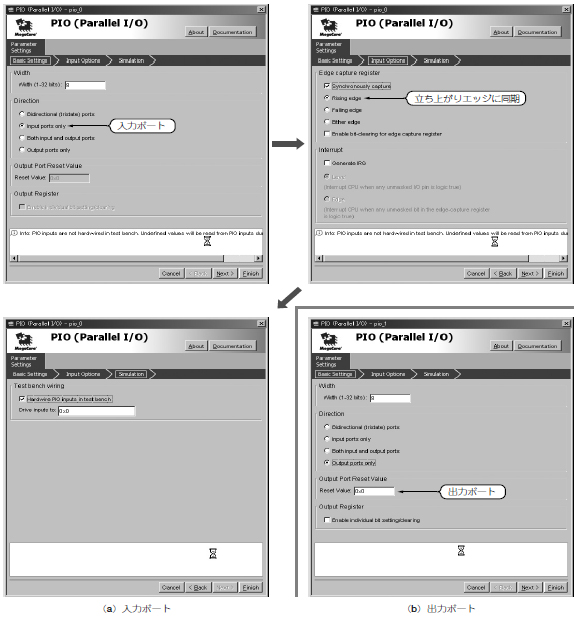

FPGAボード上にあるスイッチの読み取りには,入力ポートを使います.LED表示では,出力ポートを使って点灯/消灯を制御します.このためのパラレルI/O(PIO)をComponent Libraryから「Peripherals」-「Microcontroller Peripherals」-「PIO(Parallel I/O)」で設定します(図8).

図8 入出ポートの設定

Component Libraryから「Peripherals」-「Microcontroller Peripherals」-「PIO(Parallel I/O)」で設定する.

PIOは,1ビットから32ビット幅までの信号を一度に扱えます.データの転送方向は「入力のみ」,「出力のみ」,「方向制御付き双方向」,「方向制御なし双方向」の4種類があります.今回は,「入力のみ」と「出力のみ」の2種類の8ビットPIOコアを組み込みます.入力のみはスイッチ情報取得用に,出力のみはLED駆動用に割り当てます.

(1)スイッチ情報取得用の入力ポート

PIOの設定ウィザードの1ページ目(Basic Setting)で,バス幅はWidthを「8」,データ転送方向Directionを「Input ports only」にします.これで入力ポートになります.

ウィザードの2ページ目(Input Options)では,入力信号を内部クロックに同期させるための設定を行います.ここではEdge capture registerの「Synchronously Capture」をチェックし,「Rising edge」を選択します.

ウィザードの3ページ目(Simulation)は,シミュレーションの設定画面です.入力信号の初期値設定を有効にしておくと,警告メッセージが抑止されるため,便宜上設定しておきます.Testbench wiringの「Hardware PIO inputs in test bench」をチェックし,Drive Intuts toを「0x0」とします.

[Finish]ボタンを押すとSOPC Builderの画面に「pio_0」が追加されます.

(2)LED表示用出力ポート

PIOの設定ウィザードの1ページ目(Basic Setting)で,バス幅はWidthを「8」,データ転送方向Directionを「Output ports only」にします.出力ポートの設定はこれだけです.[Finish]ボタンを押すと「pio_1」が追加されます.

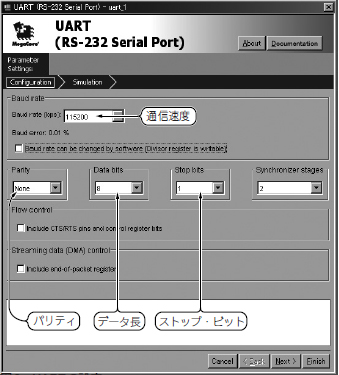

●UARTの設定

RS-232-Cなどで使うシリアル通信ポート(UART)は,Component Libraryから「Interface Protocols」-「Serial」-「UART(RS-232 Serial Port)」で設定します(図9).

図9 UARTの設定

Component Libraryから「Interface Protocols」-「Serial」-「UART(RS-232 Serial Port)」で設定する.

送信側と受信側の回路があらかじめ作り込まれており,通信速度(ボーレート)を設定するだけで,プロセッサの動作クロックから自動的に計算してくれます.例えば,115.2kbpsの転送速度が必要な場合には,通常は分周回路を作らなければなりませんが,その必要はありません.

SOPC Builderは,標準状態では動作クロックが50MHzに設定されています.今回使用するFPGAボードは,50MHzと100MHzの2種類の発振器がFPGAに接続されています.そこで本稿では50MHz発振器のクロックを使用することにします.

今回のFPGAボードには二つのシリアル・ポートがあります.このような場合は,UARTの設定作業を2回行います.

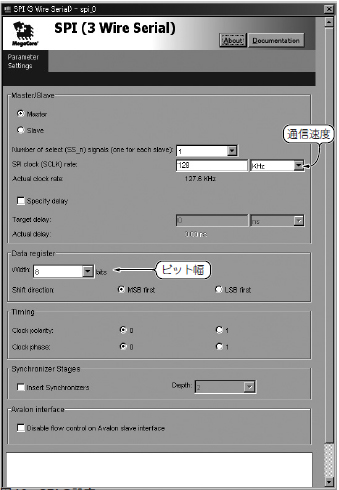

●SDカード・スロット用のSPIの設定

FPGAボードには,SDカード・スロットがあります.SDカードのインターフェースはSPIです.

Component Libraryから「Interface Protocols」-「Serial」-「SPI ( 3 Wire Serial )」で,通信速度(標準では128KHz)とデータ・アクセス・ポートのビット幅(標準では8ビット幅)を設定するだけです(図10).

図10 SPIの設定

Component Libraryから「Interface Protocols」-「Serial」-「SPI ( 3 Wire Serial )」で,通信速度(標準では128KHz)とデータ・アクセス・ポートのビット幅(標準では8ビット幅)を設定する.

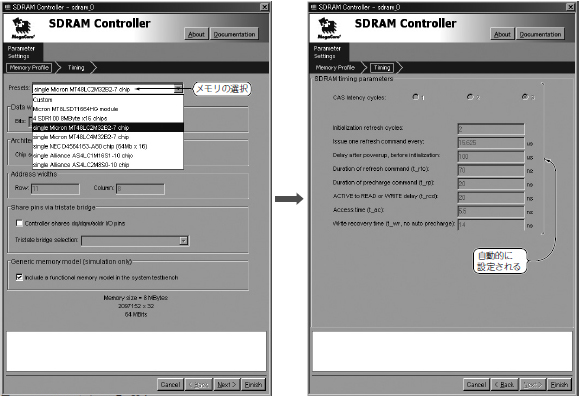

●SDRAMコントローラの設計

FPGAボードには,64Mビット(8Mバイト)のSDRAMが搭載されています.FPGAにインターフェース回路を実装することで,メモリの読み書きが可能になります.

Component Libraryから「Memories and Memory Controllers」-「SDRAM」-「SDRAM Controller」で設定します(図11).

図11 SDRAMコントローラの設計

Component Libraryから「Memories and Memory Controllers」-「SDRAM」-「SDRAM Controller」で設定する.

SOPC Builderのメモリ・コントローラ構成ツールは非常に便利です.業界で広く使われているメモリの型番があらかじめ登録されています.

FPGAボードに搭載されているSDRAMは,米国Micron Technology社の「MT48LC2M32BTG-6」です.ウィザードの1ページ目(Memory Profile)ので,Presets欄で「single Micron MT48LC2M32B2-7 chip」を選択します.

この型番を選択すると,ウィザードの画面で設定しなければならない複雑なパラメータが自動的に設定されます.通常はSDRAMメモリのデータシートに列挙されている値から最適な値を設定する作業が必要です.

特に,「Timing」メニュー内のパラメータは,けっこう面倒なものもあり,各種パラメータを自動的に計算してくれた方が楽ですし,間違いも起きません.逆に言えば,ここに登録されている型番のSDRAMを製品開発時に使用すれば,面倒な計算をせずに確実に動作する回路をすぐに用意できます.

SOPC Builderを使うと,メモリ・コントローラであっても使用するメモリの型番を選択するだけで出来上がってしまいます.

●回路にユニークなIDを付加するSystemID

Component Libraryを眺めてみると,実設計で活用したい機能がいろいろと見つかると思います.

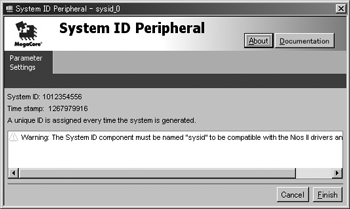

回路内に挿入しておくと何かと便利な機能としてSystemIDコアがあります.Component Libraryの「Peripherals」-「Debug and Performance」-「System ID Peripheral」で使用できます(図12).

図12 Component Libraryの「Peripherals」-「Debug and Performance」-「System ID Peripheral」で設定する.

SystemIDコアは,単純な読み出し専用のレジスタです.設計データに32ビット長の個別IDを付けることができます.コアを生成するときに,1970年1月1日からの経過時間(s)が自動的に割り出され,レジスタ内に自動的に設定されます.

SystemIDコアを設定すると,SystemIDとしてユニークな番号が割り当てられるとともに警告のメッセージが表示されます.

実はSOPC Builderで生成したコアには,名前の後ろに数値が自動的に付加されます.しかしSysIDは,名称を「SysID」にする必要があります.

そこでSOPC Builderの画面で,自動的に付加された名前の「sysid_0」をダブル・クリックし,「sysid」に変更します.