IPコアで"ラクラク"FPGA設計 <Altera編> ―― SOPC Builderを活用した基本I/O&SDRAM制御回路の設計

tag: 半導体 ディジタル・デザイン

技術解説 2010年4月23日

FPGAが主体となるシステムでは,FPGAは多くの周辺回路と接続され,このインターフェース回路の設計だけで多くの工数が必要になります.ところがFPGA開発ツールに含まれるIPコアをうまく活用すると,簡単な設定だけでこれらの回路が設計できてしまいます.ここでは,プロセッサ・コアにSDRAMインターフェース回路を素早く設計する事例を紹介します.(編集部)

最近のFPGAは,量産品にも利用されるようになりました.ディジタル回路が主体となる組み込み機器では,FPGAを中心にして製品開発を進めていく事例もあります.

本稿では,FPGAボードで用意されている周辺回路を手軽に使うために,FPGAベンダから提供されているIPコアを活用する方法を解説します.

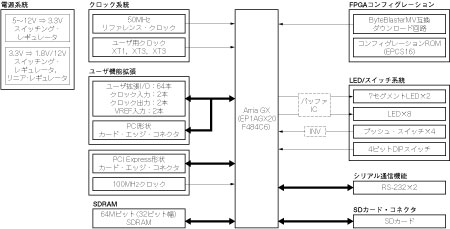

今回は,CQ出版の「Arria GX評価キット」に付属のFPGAボードを使うことを想定します(写真1).米国Altera社の「Arria GX」ファミリのFPGAを中心に,7セグメントLED,プッシュ・スイッチ,シリアル通信ポート,SDRAMなどが搭載されています(図1).また,PCIとPCI Expressバス形状のカード・エッジが付いています.

FPGAの開発には,Altera社の「Quartus II」を使用します.プロセッサ・コアを使うためには.「USB Blaster」が必要です.

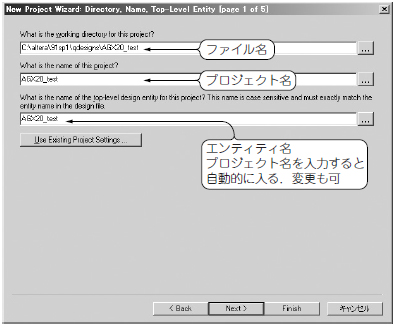

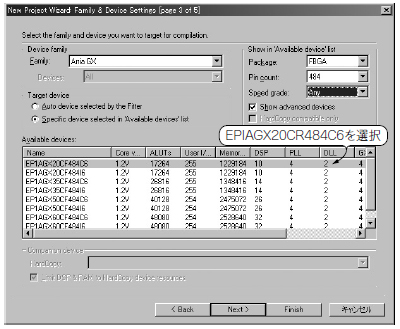

FPGAの開発は,「Quartus II」でプロジェクトを作成するところから始めます.ここでは,図2のように,プロジェクト名と最上位階層のファイル名をいずれも「AGX20_test」とします.ターゲットFPGAは,「EP1AXG20CF484C6」です.

(a)プロジェクトの設定(ウィザードの1ページ目)

(b)ターゲット・デバイスの設定(ウィザードの3ページ目)

図2 FPGAボードのブロック図

FPGAを中心に,7セグメントLED,プッシュ・スイッチ,シリアル通信ポート,SDRAMなどが搭載されている.

1. SOPC Builderによるシステム設計

SOPC Builderは,Quartus IIに含まれる機能です.Quartus IIがFPGAのコンパイルや配置配線,タイミング検証,ダウンロード機能など全体をつかさどっていることに対して,SOPC Builderは,Altera社が提供する各種ライブラリ群(IPコア)を一元管理し,FPGAに実装可能な回路を構築するために使います.

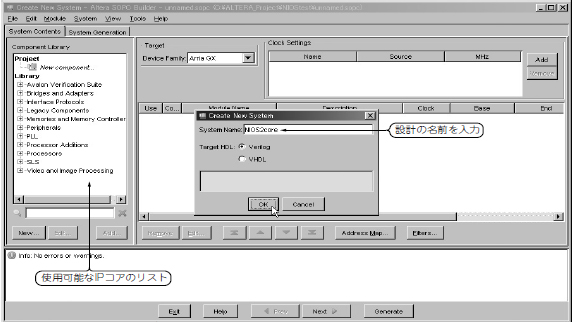

Quartus IIのメニューから「Tools」→「SOPC Builder」を選択します.SOPCBuilderを起動すると,Quartus IIに似た画面が現れます.初めに設計の名前を入力する画面が開きます.ここでは「NIOS2core」と入力します(図3).これでIPコアを使った設計ができるようになります.

図3 SOPC Builder起動

QuartusⅡのメニューから「Tools」→「SOPC Builder」で起動する.最初に設計の名前を入力する.

●プロセッサ・コアを使って全体制御

最初に,Nios IIプロセッサ・コアを使って最低限の回路を構築します(後述のコラム「Nios IIプロセッサ・コアの概要」を参照).ここでいう最低限の回路というのは,全体の制御を行うCPU,命令/データを格納するメモリ,そして開発ツールと通信する入出力機能です.

SOPC Builderの使い方は非常に単純です.左側のComponent Libraryにあるメニューが使用可能なIPコアのリストです.右側には,選択したIPコアの情報が表示されます.

●メモリの設定

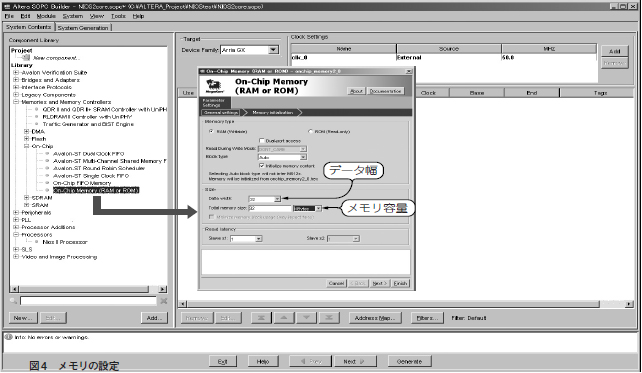

Component Libraryから「Memories and Memory Controllers」-「On-Chip」-「On-Chip Memory(RAM or ROM)」をダブル・クリックするか,選択後に[Add]をクリックします(図4).これはFPGAの内部にNios IIコア用の命令メモリを構成するためのものです.

図4 メモリの設定

Component Libraryから「Memories and Memory Controllers」-「On-Chip」-「On-Chip Memory(RAM or ROM)」を選択して設定する.

メモリの設定画面では,SRAMかROMかの種類と容量を設定します.プロセッサを使用したデバッグを行う場合には,SRAM構成で32Kバイト程度のメモリ容量を確保する必要があります.そこでSize欄には「32」,単位として「KBytes」を指定します.

ここで,Nios IIコアよりも先にメモリ・コアを設定する理由は,Nios IIコアを構成する際にリセットと例外のベクタ・テーブルを配置するメモリを指定しなければならないからです.メモリを設定する前にNios IIコアを設定すると,設定し直しの手間がかかります.

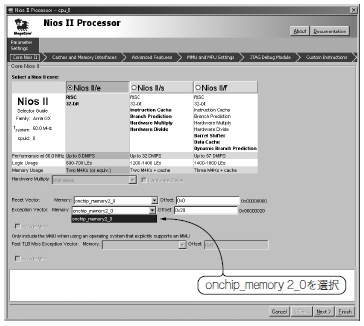

●Nios IIコアの設定

Component Libraryから「Processors」-「Nios II Processor」でNios IIコアを設定します(図5).

(a)Nios Ⅱコアの選択(ウィザードの1ページ目)

(b)デバック・モジュールの選択(ウィザードの5ページ目)

図5 Nios Ⅱコアの設定

Component Libraryから「Processors」-「Nios II Processor」を選択して設定する.

ウィザードの1ページ目(Core Nios II)の画面では,エコノミ(e),標準(s),高性能版(f)のどのコアを使用するのかを設定します.ボードのデバッグ程度であれば小型のNios II/eで十分です.

またリセットと例外のベクタ・テーブルをどのメモリ空間に配置するのかを指定します.32KバイトのSRAMが作成されていれば,プルダウン・メニューで「onchip_memory2_0」が選択できます.Reset VectorのOffsetを「0x00」,Exception VectorのOffsetを「0x20」にします.

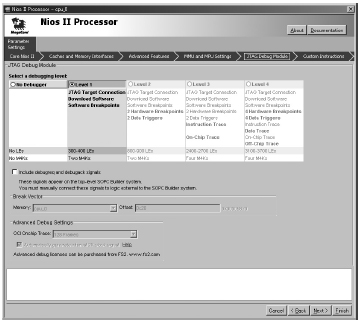

ウィザードの5ページ目(JTAG Debug Module)の画面では,Level 1が選択されていることを確認します.Level 1が選択されていれば,Altera社が提供しているソフトウェア・デバッグ環境を使うことができます.

なお,No-Debuggerは,デバッグが完全に完了した際に選択するものです.ソフトウェア・デバッグ機能が使えなくなる代わりに,回路規模が若干小さくなります(メモリ・ブロック2個+400個程度のフリップフロップ).

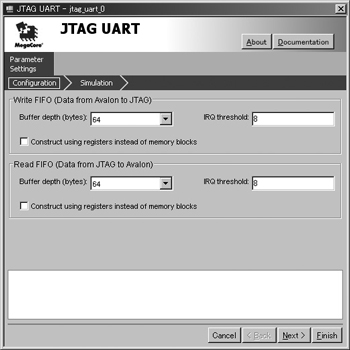

●JTAG UARTの設定

Component Libraryから「Interface Protocols」-「Serial」-「JTAG UART」で,JTAG UARTを追加します(図6).特に設定項目はありません.選択するだけで,Nios IIコアに接続可能です.

図6 JTAG UARTの設定

Component Libraryから「Interface Protocols」-「Serial」-「JTAG UART」を選択する.

プロセッサを使った場合のデバッグには,ホスト・パソコンと通信するためのシリアル・ポート・デバッグが一般的です.ただし,FPGAの場合には回路設計,基板の製造ミスや外付け部品の不具合などの影響で,はじめからFPGA内部に入れ込んだシリアル・ポート自身が確実に動くとは限りません.そこでNios IIコアには,JTAGダウンロード・ケーブルを使ったシリアル・ポート通信ができるようなっています.この機能がJTAG UARTです.

●Nios IIシステムがもう完成!

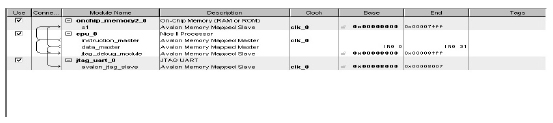

以上の三つの設定が済めば,Nios IIコアにSRAMとJTAGを用いたシリアル通信ポートが接続されたシステムが出来上がります(図7).

図7 基本的なNios Ⅱ

Nios ⅡコアにSRAMとJTAGを用いたシリアル通信ポートが接続されたシステム.

これで,開発用のパソコンとターゲットとなるFPGAボードで通信してデバッグまでできます.今回は説明を省きますが,printf関数を使ったHello World!が,このシステムで動作します.