デバイス古今東西(11) ―― FPGA設計の難しさはASIC設計を超えたのか?

「FPGA(Field Programmable Gate Array)の設計は,ASIC(Application Specific Integrated Circuit)の設計より難しくなっているのか?」.この問いに対する答えは,まだ分かりません.ただ,FPGA設計の難度は,着実に上がってきています.近年のFPGAの「高機能化」と「高速化(動作周波数の上昇)」に伴い,設計者が事前に知っておかなければならない情報の量が増えています.プッシュ・ボタン式の開発ツール(ボタンを押すだけでだれでも設計できるツール)を使用した設計の具現化が限界にきています.

ここでは,FPGA設計がどのように難しくなってきたのか,その変化を概観します.

●開発現場は年々難しくなっていることを実感

2010年1月に開催された「Electronic Design and Solution Fair 2010 (EDSFair)」にて,国内大手の通信装置メーカの主任技師の方とFPGA設計の変遷について議論したことがあります.その方によると,「FPGA設計はすでにASIC設計より難しくなっている」とのことでした.一方,筆者が取締役を任されている設計サービス会社のベテラン技術者は,「FPGA設計は,ASIC設計よりもタイミングの解析内容の自由度が低いと感じる部分がある.例えば,ASIC設計ではチップのどの部分のタイミングでも計測できるが,FPGA設計の場合はツールがある程度自動的に測定してくれる代わりに,ユーザ側で細かい個所を指定して測定することができない」と言っています.つまり,タイミング解析の柔軟性という点で,FPGA設計はASIC設計より困難であると指摘しています.

2010年時点のFPGA設計を見る限り,「ASIC設計に近い範ちゅうの作業(高度な検証作業や設計データ管理など)を実施しなければならなくなってきた分,FPGA設計はASIC設計より難度が高い場合がある」と言った方が正確だと思います.上述の技術者の話から推察できるのは,FPGA設計が年々着実に難しくなってきているということです.

●10~15年前に一つの転機があった

半導体やその設計環境の領域で実務を経験してきた筆者の記憶をたどってみると,特に1995年~2000年ころに,設計環境に大きな変化があったように思います.一つ目の変化は,設計環境を構成するコンピュータがエンジニアリング・ワークステーションからパソコンへ移行したことです.二つ目の変化は,設計入力の方法がゲート・レベルの図面入力からRTL(Register Transfer Level)のハードウェア記述言語(HDL)による入力へ移行したことです.三つ目の変化は,ASIC一辺倒だったカスタムLSIの設計がFPGAとASICの双方を見据えた設計に移行したことです.2000年以降,パソコンの上で設計環境を動かし,HDLを用いてFPGAを設計するやり方が定着したのです.

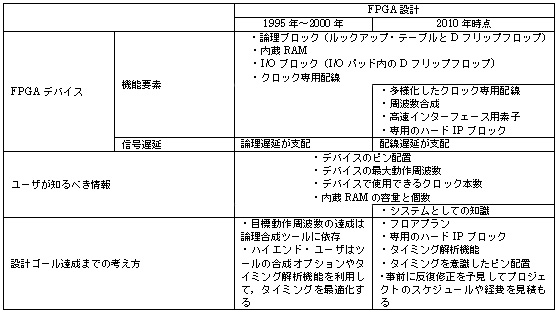

この変化から10年がたちました.FPGAの設計環境を1995年~2000年と現時点の2010年という時間軸で対比してみると,何が変わってきたのでしょう.「FPGAデバイス」,「ユーザが事前に知っておかなければならない情報」,「設計ゴール達成までの考え方」という三つの視点で整理してみます.

●FPGAデバイスの構成要素は複雑に

「FPGAデバイス」について見ていきましょう.

1995年~2000年のFPGAの機能は,主に四つの要素で構成されていました.すなわち論理ブロック(ルックアップ・テーブル+Dフリップフロップ),内蔵RAM,I/Oブロック(I/Oパッド内のDフリップフロップ),クロック専用配線の四つです.そして,信号遅延については,配線遅延ではなく論理遅延(素子遅延)が支配的でした.

2010年時点のFPGAの機能は,上記の四つの要素に加えて,多様化したクロック専用配線,周波数合成,高速インターフェース用素子,そして専用のハードIPブロックがあります.

多様化したクロック専用配線には,I/Oパッド部の専用クロック,駆動可能な領域が限定されたローカル・クロック,FPGA全域を駆動できるクロックが含まれます.

周波数合成は,PLL(Phase-locked Loop)やDLL(Delay Locked Loop)などの回路を指します.これらの特性はデバイスごとに異なります.例えば,クロックてい倍やクロック分周,シフトの有無といった機能,ジッタ量,入力/出力可能な周波数,といった特性です.

高速インターフェース用素子とは,DDR(Dual Data Rate)用Dフリップフロップ,入力/出力の遅延調整用素子,I/Oパッド領域に組み込まれる機能素子などを指します.

専用のハードIPブロックには,代表例として高速シリアル通信用トランシーバ回路(SerDes,RocketI/Oなど)やPCI Express用インターフェース回路,DDRメモリ用インターフェース回路,ディジタル信号処理ブロック,組み込みプロセッサ・コアなどがあります.

信号遅延については,1995年~2000年と2010年では状況が異なっています.プロセスの微細化によって支配的な遅延の要素が逆転し,論理遅延より配線遅延の影響が大きくなっています.

●デバイスや回路だけでなくシステムそのものの知識が必要に

次に,「ユーザが知るべき情報」について見ていきましょう.

1995年~2000年の時点では,主としてデバイスのピン配置や最大動作周波数,デバイスで使用できるクロック本数,内蔵RAMの容量と個数などを,把握しておく必要がありました.

2010年の現在は,これらの情報のほかに,高速シリアル通信用トランシーバ回路,高速インターフェース回路,専用のハードIPブロックなど,FPGAのファミリごとに異なる各種機能やそれらの特性,実際に具現化する上での制約事項などを知っておく必要があります.例えば,FPGAのクロック配線や専用回路素子などについて,使用できるリソースが限られています.また,デバイス・ファミリによってその特性や制約事項が異なっています.従って,使用するデバイスの特性や制約事項をよく理解した上で設計しないと,カタログに記載されている高い性能を引き出すことができません.

さらに,組み込みプロセッサ・コアなどの専用のハードIPブロックを利用する場合は,システム知識も求められます.システム知識とは,機器を構成するさまざまな技術要素とその関係についての情報です.つまり,現在のFPGA設計ではデバイスや回路の知識だけでは不十分で,機器そのもの知識が必要になるということです.

●設計ゴールを達成するために数多くの対策を組み合わせる

最後に,「設計ゴール達成までの考え方」について見ていきます.

1995年~2000年ころは,目標となる動作周波数の達成が最優先事項の一つでした.しかしその可否は,あくまでも論理合成ツール頼みでした.ハイエンド・ユーザは,論理合成ツールのさまざまなオプション設定を駆使してタイミングの最適化を図っていました.例えばタイミング解析によりクリティカル・パスを検出し,その遅延に対策を施していました.

動作周波数やゲート利用率が低い場合は,上述のような10年前の設計手法でも対応可能です.しかし2010年の現在では,プッシュ・ボタン式の開発ツールだけでタイミングを最適化することが難しくなっています.そして,さまざまな手法を駆使しなければならない状況にあります.以下では,いくつかその例を挙げてみます.

一つ目の手法はフロアプランです.これは,デバイス上の論理ブロックや配線要素の概略をグラフィカルに表示し,必要に応じてユーザが調整する工程です.フロアプランを行う際には,FPGAのデバイス構造とクロック・ネットワークの知識が必須です.

二つ目は,専用のハードIPブロックの利用です.組み込みプロセッサ・コアなどのハードIPブロックを使用する場合,そのブロックのシステム・レベルの知識が必要となります.

三つ目は,動作周波数の高速化に伴うクロック配線やPLLなどの接続構成,および高度なタイミング解析機能の活用です.これは,クロック・ジッタやクロック・スキューがタイミングを満たせない要因となってきているからです.

このほか,DDRメモリ・インターフェースなどの高速I/Oを用いる場合は,タイミングを意識したピン配置が必須です.I/OピンからI/Oパッド内のDフリップフロップまでの遅延差が致命的な問題となりうるので,データ信号とストローブ信号について,こうした信号遅延が同じになるようなピン配置を検討しなければなりません.

クリティカル・パス対策は,もはや論理合成ツールだけで解決することはできません.HDL記述の修正の繰り返しを想定しておく必要があります.つまり,論理合成,検証,配置配線の一連のフローの反復修正を前提として設計にのぞまなければなりません.さもなければ,開発スケジュールや経費などの管理が破たんしてしまいます.

* * *

上記で述べた内容を,表1に簡単に整理しておきます.

表1 FPGAの設計環境の対比

◆筆者プロフィール◆

山本 靖(やまもと・やすし).半導体業界,ならびに半導体にかかわるソフトウェア産業で民間企業の経営管理に従事.1989年にVHDLの普及活動を行う.その後,日米で数々のベンチャ企業を設立し,経営責任者としてオペレーションを経験.日米ベンチャ企業の役員・顧問に就任し,経営戦略,製品設計,プロジェクト管理の指導を行っている.慶應義塾大学工学部卒, 博士(学術)早稲田大学院.