HDL時代に求められる論理回路設計とは ―― 回路記号を使わない設計手法の考え方

tag: 半導体 電子回路 ディジタル・デザイン

技術解説 2009年11月 6日

ハードウェア記述言語を用いる大きな利点は,設計の抽象度が上がることとコンピュータで動作する設計ツールを活用できることです.つまり実務で求められている技術は,多くの教科書に書かれているような,論理ゲートを組み合わせて回路図を記述する手法とは異なります.本稿では,現代にマッチした論理設計技術を解説していきます.ここでは,今実務で求められている設計手法とその学習法を明確にします.また,論理回路設計で最低限必要な数学を復習します.(編集部)

本稿では,できるだけやさしく論理回路の設計技術を解説していきます.内容は簡単でも,時刻合わせができる時計を作ったり,パソコンとデータをやりとりする「シリアル送受信回路」を作ったりなど,達成目標は高度です.

「やさしく」と「高度」を両立するため,抽象度を一つ上げたところから学習を始めます.従ってゲートやフリップフロップによる回路は一切出てきません.言語によって論理回路を設計する現在では,論理回路の学習スタイルも従来と変わってきてよいはずです.この章では言語設計時代の学習スタイルについて説明します.

1.HDL時代の設計手法と学習法

●回路記号を使わない論理設計手法の提案

論理設計の手法が,回路図からハードウェア記述言語に変わり始めてからずいぶんたちます.当初ハードウェア記述言語による設計は,限られた分野だけ使われていましたが,10年ほど前からFPGAなどでもごく普通に使われるようになってきました.最近ではCベース言語を用いた論理設計も,珍しいものではなくなっています.

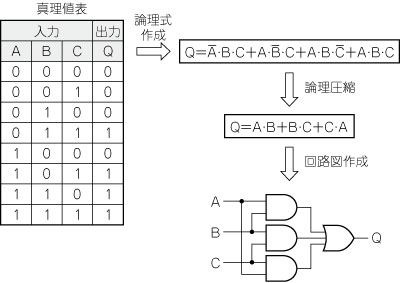

しかし論理回路設計を学ぶ方法といえば,論理を式で表し,回路記号を並べて設計を行うスタイルばかりです(図1).多くの論理回路の教科書は言語設計を前提としていないので,このようなスタイルになってしまいます.学習する方々も,カウンタやシフト・レジスタの動作を学んだあたりで息切れしてしまうでしょう.

図1 回路図を用いた設計手法

多くの論理回路の教科書は言語設計を前提としていないので,論理を式で表し,回路記号を 並べて設計を行うスタイルになってしまう.つまり,この手法は言語設計では非効率になる.

これでは機能的にまとまった回路を設計できるようにはなりません.何年も英語を学んでも,満足に会話できない状況によく似ています.

基礎を学ぶという意味では,ブール代数なども大事ですが,論理圧縮はもはや人手でやるものではありません.回路記号を並べて設計することも非効率です.

規模が大きく機能が複雑な回路を設計できるようになるためには,効率的な学習方法があるはずです.そこで本稿では回路記号を使わない論理設計手法を解説します.

●論理設計に徹する…部品の知識は後回し

「部品割り当て設計」とは,論理回路を実現する対象に合わせた設計をすることを意味します.

回路を設計するということは,動くものを作るということです.つまり,実際に動作しなければ意味がありません.そこで回路図には,仕様を実現する「論理」だけでなく,実際の「部品」を想定した部分も含まれます.つまり回路図には,論理を部品に割り当てるための情報が含まれることになります.

いくつか例を示します.

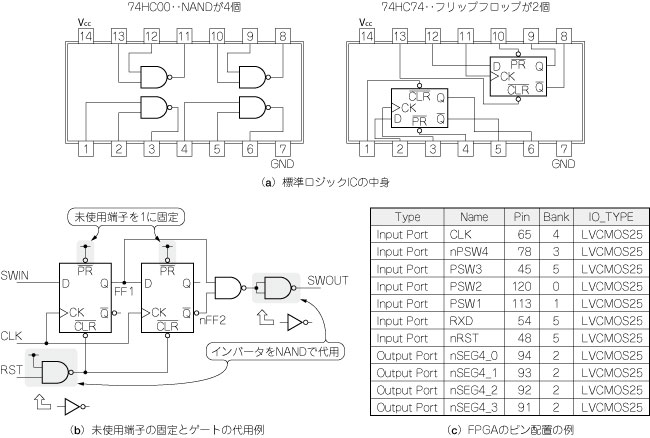

(1)標準ロジックICの場合

標準ロジックICは,複数個の論理素子が一つのパッケージに含まれているようなICです(図2-a).このような部品を使う場合には,部品に合わせた設計が必要になります.図2-(b)に示すように,フリップフロップの未使用端子(この場合はプリセット端子PR)を'1'に固定したり,使用するICの数を減らすためNANDゲートをインバータ代わりにすることなどです.実際にこの回路では,図2-(a)に示した部品が1個ずつあれば実現できます.

図2 部品割り当てによる設計

標準ロジックICを用いた回路では,フリップフロップの未使用端子を'1'に固定したり,使用するICの数を減らすためのNANDゲートをインバータ代わりにすることがある.FPGAではピン配置を決める必要がある.このように「部品」を考えることは論理設計の本質ではないので後回しでよい.

(2)FPGAの場合

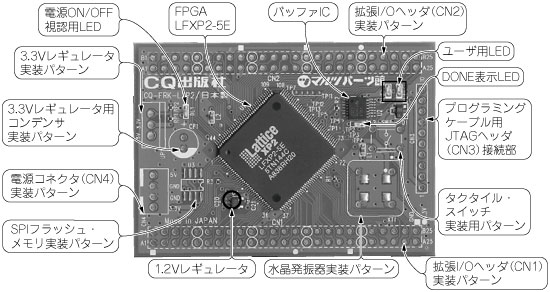

『ディジタル・デザイン・テクノロジ』誌(2009年No.1)に付属されたFPGA基板(写真1)を使う場合,

- FPGAメーカの提供する開発環境を使いこなす

- 実装された基板に合わせて端子割り当てをする

- 入出力端子が'1'か'0'のどちらで機能するのかを調べ,これに合わせて論理を設計する

ことなどが必要です.

写真1 『ディジタル・デザイン・テクノロジ』誌(2009年No.1)に付属のFPGA基板

米国Lattice Semiconductor社のLatticeXP2を搭載している.

FPGAに接続したクロック入力やスイッチ入力を有効にするには,図2-(c)のように,基板上の接続に合わせて正しくピン配置を設定する必要があります.さらにリセット端子nRSTやスイッチ入力nPSW4は'0'で動作しますので,内部の論理もこれに合わせて設計する必要があります.これらも設計工程に含まれますが,純粋な論理設計とは異なります.

最終的にモノを作る上では,実現する対象を考慮しないで設計するのは餅を絵に描いているだけにすぎません.しかし論理回路設計を学ぶ上では,「部品」の部分は後回しにして純粋に論理だけを追う学習をすべきだと思います.

本稿で紹介する回路例は,大半がFPGAで動作可能です.しかし「部品割り当て設計」の部分は,階層を分けることで吸収していますので,ここでは論理だけ考えればよいように解説していきます.

●論理と遅延を分けて考える…遅延も後回し

論理回路は電子回路でもあるので,信号が伝達する経路において必ず遅れが発生します.回路図で設計していたころは,この遅延を考慮した上で設計する必要がありました.論理を考えると同時に,遅延関係も考慮して設計していました.

しかし言語設計では論理の実現を主として行い,回路表現の中に遅延の情報を盛り込まずに設計します(図3).これができるようなった理由は以下のようなものがあります.

- 以前は回路規模を小さくするのが最優先であり,そのため遅延関係に厳しい回路構造にせざるを得なかった

- 現在では回路規模が最優先でなくなったので遅延関係に依存しにくい回路構造を使えるようになった

- 遅延関係を満たすことが,論理合成ツールにより自動化できるようになった

- 論理素子の遅延量が極めて短くなり,遅延が問題になる状況が少なくなった

とはいえ,遅延をまったく無視して設計できるわけではありません.論理合成ツールを駆使しても遅延関係を満たせず,構造から見直すこともあります.慣れた設計者になれば,遅延を含まない言語設計でも最終的に得られる回路の遅延を想定して回路構造を決めることもできます.

図3 遅延と論理に分けて考える

言語設計では論理の実現を主として行い,回路表現の中に遅延の情報を盛り込まずに設計する.