半導体チップの静電気放電による不良を製造と設計の両面から低減 ―― EOS/ESD Symposium 2009レポート

過電圧・過電流ストレス(EOS:Electrical Overstress)と静電気放電(ESD:Electrostatic Discharge)が半導体デバイスや電子システムなどに与える影響を議論する国際学会「EOS/ESD Symposium 2009」が2009年8月31日~9月4日に米国カリフォルニア州AnaheimのDisneyland Hotelで開催された(写真1).EOS/ESD Symposiumは毎年秋に米国で開催されており,今回で第31回となる(写真2).

写真1 EOS/ESD Symposium 2009会場のDisneyland Holtel

写真2 米国の業界団体であるESD AssociationがEOS/ESD Symposiumを主催してきた

EOS/ESD Symposiumは,一般講演とチュートリアル(セミナ)講演,ワークショップ(討論会),展示会などで構成されている.本レポートでは一般講演と展示会を中心に,各トピックスを紹介する.

●デバイスの組み立て工程でESDの発生を防ぐ

ドイツのInfineon Technologies社は,半導体デバイスの組み立て工程におけるESDの危険性を調査した結果を報告した(講演番号1B.2).組み立て工程には,シリコン・チップ(ダイ)や樹脂封止済みのデバイスを取り扱うさまざまな設備が存在する.しかし,設備メーカの多くはESDの危険性を認識しておらず,また,危険性を認識していたとしてもどのような対策が適切であるかの知識を持ちあわせていないと指摘した.

半導体デバイスの組み立て工程でESDが問題になるのは,シリコン・チップ(ダイ)が何らかの原因で帯電し,その後に金属と接触して放電が起こる場合が多い.放電によってダイの回路にパルス状の電流が流れ,回路を破壊する.帯電のほとんどは摩擦によって起こる.組み立て工程は機械的な加工を伴うので,摩擦帯電を避けることは難しい.そこで,シリコン(またはリード端子)と金属の接触放電が起こりそうな個所に絞って対策を施すことになる.

Infineon Technologies社は講演で,ESD不良の具体的な事例を三つほど紹介した.最初の事例は樹脂封止パッケージのリード曲げ加工工程である.曲げ工程でシリコン・チップ(ダイ)の帯電が原因とみられるESD不良が発生した.

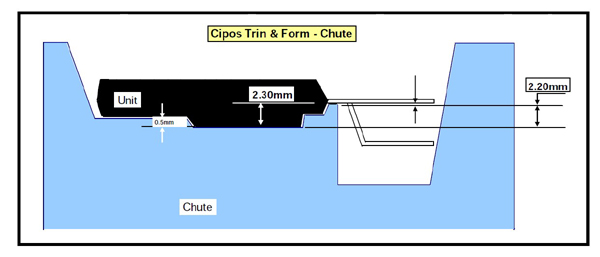

リード曲げ工程ではあらかじめパッケージを固定し,金型でリードを折り曲げる.リードと金型のクリアランスはわずかで,0.1mmしかない(図1).このクリアランスが曲げ加工によってゼロになり,リードと金型の接触放電を招いていた.そこで金型表面を酸化することで絶縁体とし,放電を防いだ.この事例では設備メーカはESDの危険性を認識しており,イオン・ブロワによって帯電防止策を施していた.しかし具体的な危険個所の認識までには至っておらず,イオン・ブロワが効果的な対策とはなっていなかった.

図1 リード曲げ加工装置の各部寸法

リードと金型のクリアランスは0.1mmしかない.

2番目の事例は,半導体テスタである.このテスタは「ESDオプション」と呼ぶESD対策オプションが存在し,イオン・ブロワによって帯電を防ぐ仕組みが装着してあった.しかし,樹脂封止パッケージをトレイから金属製容器に移動させる個所で,シリコン・チップ(ダイ)の帯電が原因と推定される半導体デバイスのESD不良が発生した.

調査の結果,以下のようなメカニズムで不良が発生していた.樹脂封止パッケージをトレイから吸引タイプのキャップで持ち上げるときに,樹脂が帯電する(誘導によってシリコンのダイも帯電する).そして金属製容器とパッケージのピンが接触し,放電が起こる.帯電から放電までの時間はきわめて短いので,イオン・ブロワでは帯電をほとんど中和できなかった.ここで重要なのは,イオン・ブロワによる中和には一定の時間を必要とすることだ.結局,金属製容器の表面を酸化処理して絶縁体とすることで,接触放電を防ぐことにした.

3番目の事例は,プリント基板組み立て工程である.車載用エアコンの制御基板組み立て工程で,半導体デバイスの不良が発生した.この半導体デバイスはシリコン・チップ(ダイ)の帯電によるESDの耐性が高い品種であったにもかかわらず,ダイの帯電が原因と思われる不良が発生した.具体的には,トランジスタのゲート酸化膜が破壊されていた.ESD不良はプリント基板の最終テスト工程で発生し,不良が発見されたのは最終テスト工程であったり,車載用エアコンにプリント基板を取り付けた後であったり,車載用エアコンが車両に装着されてエンド・ユーザに販売された後であったりした.

プリント基板テスタの治具は金属製であり,治具は10枚のプリント基板を同時に持ち上げてテストにかけていた.ここで不運にも,プリント基板のヒートシンクが治具に接触していた.このため,治具とプリント基板の両方が数百Vに帯電した.そしてテスタの測定電極がプリント基板のコネクタ電極と接触することで放電が発生し,トランジスタのゲート酸化膜が損傷を受けていた.そこで治具の帯電を防ぐために,治具を接地することにした.ただし直接治具を接地するのではなく,10MΩと高い抵抗を介して接地した.接地抵抗を高くしたのは治具が帯電して放電が発生したとしても,放電電流をゆっくりと流すことでピーク電流を低減するためである.

●レイアウト設計でESD耐性を高める

オランダのNXP Semiconductors社は,半導体チップの回路レイアウトから,ESDに弱い個所を見つけだすチェック・ツールを開発した(講演番号4A.2).米国Mentor Graphics社のレイアウト検証ツール「Calibre」とともに動作する.

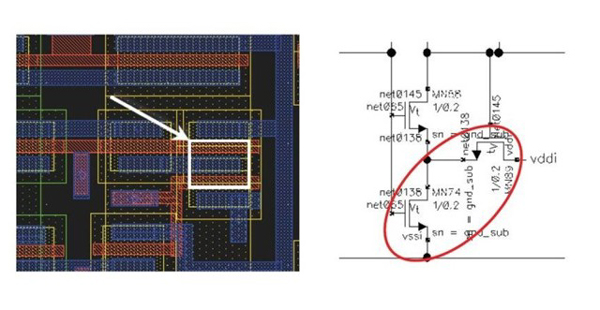

ESDによって問題を起こす個所の大半は,寄生バイポーラ(npnバイポーラまたはpnpバイポーラ)である.開発したチェック・ツールは,GDS形式のレイアウト・データを入力すると,ESD耐性の低い寄生バイポーラを自動的に見つけてくれる.リストアップされた寄生バイポーラを回路技術者が詳細にチェックすることで,レイアウトの修正が必要な個所を洗い出せる(図2).

図2 ESD耐性の低いレイアウトの例

図2 ESD耐性の低いレイアウトの例

左はレイアウト.同じアクティブ領域に2個のnチャンネルMOSトランジスタが配置されている.右は回路図.電源線と接地線の間を2個のMOSトランジスタでカスコード接続した(赤い楕円で囲んだ部分).

講演では,複数のウエル(nウエルおよびpウエル)によって生じた寄生バイポーラを見つけた例や,90nmのSoC(System on a Chip)設計にチェック・ツールを適用してESD耐性の低い寄生バイポーラを見つけ出した例などを報告していた.

●高速インターフェース向けのESD保護デバイス

展示会では,高速インターフェース向けのESD保護デバイスの展示が興味深かった(写真3).NXP Semiconductors社と米国CMD(California Micro Devices)社がそれぞれ,ESD保護デバイスを出展していた(写真4).HDMI(High-Definition Multimedia Interface)やUSBなどのコネクタ付近に実装し,ESDなどの過電圧サージから受信ICを保護する.

写真3 展示会の会場風景

写真4 NXP Semiconductors社によるESD保護デバイスの展示

ESD保護デバイスは通常,ダイオード・アレイによる電圧クランプ回路と電流シャント回路で構成される.例えばピーク電圧8kVの過電圧サージを,8Vの低い電圧にクランプする.ダイオードを使っているので,バリスタに比べると内部インピーダンスが低いという特徴がある.高速データ伝送デバイスや発光デバイス,化合物半導体デバイスなどは本質的にESDに弱い.ESD保護デバイスの必要性はますます高まる傾向にある.

ふくだ・あきら

テクニカルライター/アナリスト

http://d.hatena.ne.jp/affiliate_with/