アーキテクチャの検討段階でチップ面積や消費電力を見積もるツール「InCyte」 ―― Cisco Systems社が二つのASICで評価,面積誤差は10%以内

「LSI開発の企画段階において,面積や性能,消費電力などを見積もることができたら...」.こうした要望に応えるツールとして,さまざまなデザイン・プランニング・ツールが商用化されている.しかし,こうした見積もりツールには,見積もり精度と計算時間(あるいは,必要な情報を用意するために要する時間)の間のトレードオフの問題がある.さらに,LSI設計ツールの常として価格が高く,気軽に評価することができない.ここでは,Webサイトからスタータ・エディションを無償でダウンロードできる「Cadence InCyte Chip Estimator」を紹介する.専用のWebサイト(http://www.chipestimate.com/)では,本ツールに関連するIPコアなどの情報が公開されている.(編集部)

Cadence InCyte Chip Estimator (以下,InCyte)は,LSI開発の企画段階においてチップ・サイズや動作周波数,消費電力を見積もるためのツールです.米国Cadence Design Systems社が開発しました.対象ユーザは,LSIのアーキテクト,設計者,プロジェクト責任者,RFQ(Request For Quotation)担当のビジネス営業,テクニカル・マーケティングなど,幅広い層を想定しており,こうしたユーザを意識してGUIや使い勝手が調整されています.

本ツールを利用すると,RTL(Register Transfer Level)データ,ゲート・レベルのネットリストといった設計データがまだ存在しない段階で上述の見積もり作業を行えます.

●アーキテクチャの最適化や仕様策定の際の指針になる

InCyteは,Windows,Linux,SolarisといったOSの上で動作します.InCyteのスタータ・エディションは「ChipEstimate.com 」という,Cadence社が運営するWebサイトから無償でダウンロードできます(図1).ぜひ,手元のパソコンにインストールしてみてください(ユーザ登録が必要).

なお,スタータ・エディションは機能限定版です.選択可能なプロセスは,特定のファウンドリのプロセスではなく,業界の65nmノードを平均化したものに限定されています.そのため,見積もり結果の精度は製品版のものとは異なります.さらに,動作周波数やコストの見積もり機能も省かれています.

図1 ChipEstimate.comのトップ・ページ

ユーザは,使用するIPコアやメモリ,プロセス・ノード,階層構造,論理ゲート数,クロック,メモリ・ビット数,I/O数,LSIパッケージなどの情報を入力します.これらの情報をもとに,InCyteはチップ・サイズや動作周波数,消費電力(ダイナミック電力,リーク電力),コストなどを計算します.見積もりの計算は数秒で終わります.

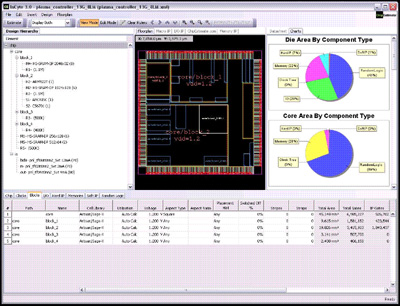

図2はInCyteのGUIです.画面上側の左がチップの階層構造を,中央がフロアプランを,右が面積の比較を示しています.画面下部のスプレッド・シートに,開発するチップやIPコアの各種仕様を入力します.

本ツールを利用すると,入力値を変更した場合の見積もり結果の比較を容易に行えます.例えば使用するプロセス・ノードを90nmから65nmに変更したり,バス構成や接続するIPコアを別のものに変更したとき,チップ・サイズや消費電力がどれだけ変化するかを確認できます(いわゆるwhat-if解析).また,コストの計算については,テストやパッケージ,マスク,ウェハなどの業界平均価格,および期待できる歩留まりをもとに見積もっています.こうした情報は,アーキテクチャの最適化や設計仕様策定の際にとても参考になります.

●IPコアや回路ライブラリのポータル・サイトと連携

InCyteを利用する場合,IPコアや回路ライブラリの情報が不可欠です.そこでChipEstimate.comでは,これらの情報を容易に検索できるようにしています.

ChipEstimate.comにはIP ベンダやファウンドリなど200 社以上が提供する7,000 種類以上のIPコアが登録されています.ユーザはこれらの情報を検索したり,比較したりすることが可能です.2009年8月時点の登録ユーザ数は約22,000名です.また,ChipEstimate.comはCommon Platform(米国IBM社,韓国Samsung Electronics社,Chartered Semiconductor Manufacturing社が共同開発した半導体プロセス,およびその設計環境)や台湾TSMC(Taiwan Semiconductor Manufacturing Co.)など,主要ファウンドリの標準的なIPデータベースとしても活用されています.

IPコアのユーザは,ChipEstimate.comにIPコアのキーワードを入力して必要な情報を探します.例えば論理ゲート数や消費電力,I/O数,使用実績などの基本情報やデータシートを本Webサイトから入手できます.代表的なファウンドリについては,製造プロセスを指定することにより,そのプロセスに合わせて開発されたIPコアや製造実績のあるIPコアを検索することも可能です.こうして探し出したIPコアは,InCyteのIPブラウザからドラッグ&ドロップすることで,見積もり対象として取り込むことができます.

IPコアを外販するベンダにとっては,本サイトにIPコアを登録することにより,宣伝や営業支援に活用できます.

●Cisco Systems社が二つのASICのデータを利用して評価

次に,InCyteの利用例を紹介しましょう.ネットワーク機器大手の米国Cisco Systems社が利用・評価した例です.同社では,チップ・サイズ,消費電力(ダイナミック電力,リーク電力),およびコストの見積もりをアーキテクチャ検討の段階で行っています.同社がInCyteを使用するにあたって確認したかったポイントは以下の3点です.

- InCyteによって実際のシリコン・チップに近い見積もりを行えるか

- 見積もり結果に矛盾がないか(一貫性があるか)

- 高速にwhat-if解析を行えるか

同社は,既に開発済みの二つのASIC(Application Specific Integrated Circuit)を選定し,実際のシリコンに対してInCyteの見積もり結果が合致しているかどうか,さらに同社がこれまで使用していたチップの見積もり手法の結果と差があるかどうかを評価しました.同社が期待したのは,InCyteによるチップ・サイズの見積もり誤差が実際のシリコン・チップに対して10%以内に収まることでした.

二つのASICの製造プロセスはTSMCの130nm LV(Low Voltage),配線層数は8でした.また,スタンダード・セル・ライブラリには英国ARM社のArtisan LV SAGE-Xを,I/Oパッドにはサード・パーティ製のものを,メモリには米国Virage Logic社のSTAR Memory Systemを用いています.

以下に二つのASIC(Bridge ASIC,Port ASIC)の仕様を示します.

● Bridge ASIC

-570万ゲート

- 11.9Mビット・メモリ(合計ビット数)

- 3.6MビットSRAMブロック×2個

- 6.7MビットSRAMブロック×1個

- 1.6Mビットのレジスタ・ファイル

● Port ASIC

- 680万ゲート

- 4.36Mビット・メモリ(合計ビット数)

- 3.2MビットSRAMブロック×1個

- 1.16Mビットのレジスタ・ファイル