アーキテクチャの検討段階でチップ面積や消費電力を見積もるツール「InCyte」 ―― Cisco Systems社が二つのASICで評価,面積誤差は10%以内

●自社開発のIPコアについては事前の登録が必要

見積もりを行いたいASICの情報がそろったら,これらをInCyteに入力していきます.GUIを利用して,ランダム論理のゲート数,クロック,I/O,メモリなどの情報を登録します.InCyteのIPブラウザから,ターゲット・プロセス向けに開発されたサード・パーティ製のIPコアの情報を参照できます(図3).そこから使用したいIPコアを選択し,追加登録していきます.

Cisco社の場合,ASICを構成する回路ブロックの中に自社で開発したIPコアが含まれていました.この場合,自社開発のIPコアをローカルIPとしてInCyteに登録し,IPブラウザから選択・設定する必要がありました.

このほか,テクノロジ・ノードやライブラリなどの情報を入力します.なお,これらの情報は,Excel経由で取り込むこともできます.

図3 InCyteのIPブラウザ(ここで選択可能なIPコアはChipEstimate.comにて閲覧可能)

Cisco社が入力した情報は以下のとおりです.

- テクノロジ(テクノロジ・ノード,ファウンドリ・プロセス,メタル層)

- スタンダード・セル(RTLやソフトIPのライブラリ・セル)

- I/Oフレーム(I/Oパッド・セルとボンディングのルール)

- メモリ(特定のサイズとタイプ)

- ハードIP(ディジタル,ミックスト・シグナル,アナログ)

- ソフトIP(サード・パーティ製,自社開発のIPコア)

●数秒で見積もり完了,結果はレポートやEDAファイルとして出力

必要な情報の入力が完了したら,見積もりを実行します.見積もりの計算に要する時間は,平均で3~10秒程度です.InCyteは,IPベンダやファウンドリが提供するデザイン・キットの内部モデルを利用しており,精度の高い見積もりが行えます.これらのモデルには,IPコアやセルのサイズ,消費電力などの情報が含まれています.スタンダード・セルやI/Oのライブラリ・フォーマットについては,米国Synopsys社のLibertyファイルやCadence社のLEFファイルなどに対応しています.

チップ・サイズの見積もりアルゴリズムには,動作周波数ベースのセル占有率モデルを利用しています.下位階層の回路ブロックのサイズについては,使用するスタンダード・セル,トリガを与えるクロック信号の周波数,混載するIPコアやメモリ・ブロックなどを考慮して計算しています.サード・パーティ製のメモリについては,メモリ・コンパイラによってモデリングされたサイズ,消費電力,性能(タイミング)の情報をもとにして計算しています.

見積もり結果のレポート(データシート)は,HTML,PDF,CSVで出力されます(図4).こうしたレポート以外に,以下のファイルを出力します.

- 簡易フロアプラン(DEF)

- IPコアやメモリなどのハード・マクロ用フィジカル・ライブラリ(LEF)

- 上位階層のVerilog HDLネットリスト

- タイミング制約(SDC)

- 消費電力(CPF)

- Spirit IP-XACT

- インプリメンテーション用スクリプト(合成ツール用,配置配線ツール用)

- メモリ・コンパイラ用スクリプト

これらの出力ファイルは,その後のインプリメンテーション工程におけるプロトタイピングや論理合成,フロアプラン,配置配線などのEDAツールで利用できます.

図4 レポートの出力例

見積もり結果のレポートには,各階層の回路ブロックの詳細なサイズ,消費電力,IPコアやI/Oの占有面積から簡易フロアプラン図まで掲載されます.また,パイ・チャートにより,面積や消費電力についてどの部分が支配的かを容易に判断できます.

ゲート数やセル使用率(占有率),クロックなどの情報が分かっている場合には,これらを入力したほうが見積もり精度は上がります.Cisco社がこのツールを使用した際には,Cadence社がこうした追加情報を入力する手段を提供して,見積もり精度を向上させました.

●面積の見積もり誤差は6~8%にとどまる

Cisco社はコア領域の総面積,およびメモリやハード・マクロ,スタンダード・セルの面積を比較しました.実際のシリコン・チップとInCyteの見積もり結果はほぼ合致し,仕様入力に要した時間は数分程度でした.

Bridge ASICの見積もり結果を表1に示します.実際のシリコン・チップより6.7%大きく見積もっていることが分かります.

表1 Bridge ASICの見積もり結果

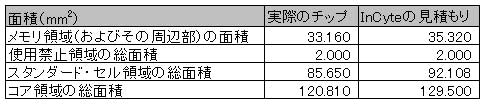

Port ASICの見積もり結果を表2に示します.実際のシリコン・チップより7.2%大きく見積もっていることが分かります.

表2 Port ASICの見積もり結果

Cisco社は,InCyteの見積もり結果に対して好印象を持ったそうです.前述のとおり,このツールに追加情報を入力することで,見積もりの精度を向上させることができます.実際のシリコン・チップに対して,10%以内の誤差で見積もりを行えることを確認できました.

見積もりの計算は数秒で完了しました.つまり,チップの仕様に変更が生じたときに,アーキテクトや設計者は即座に見積もりの再計算を行えます.それらの変更をサイズや消費電力,コストの見積もりに反映できます.例えば,動作周波数を引き上げたら消費電力がどれだけ増加するか,あるいは製造プロセスを130nmから90nmへ変えたらチップ・サイズがどれだけ小さくなるか,といったことを見積もれるのです.

参考URL

(1) ChipEstimate.com:http://www.chipestimate.com/

(2) InCyteスタータ・エディションのダウンロード・ページ(要ユーザ登録):http://www.chipestimate.com/download.html

(3) ChipEstimate.comとInCyteの日本語紹介ページ:http://www.cadence.co.jp/log/bana2/

(4) IP検索サイト「ChipEstimate.com」とチップ見積りツール「Cadence InCyte Chip Estimator」(Cadence社の広報誌「THE SOUND OF CADENCE Vol.69」の掲載記事):http://www.cadence.co.jp/soc/soc-69/69-7.html

(5) Cadence社製品についての問い合わせ先:http://www.cadence.co.jp/contact/index.html

はしもと・ともゆき

日本ケイデンス・デザイン・システムズ社 カスタマ・プラットフォーム・マーケティング部