初めてでも使えるVHDL文法ガイド ―― 記述スタイル編

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月27日

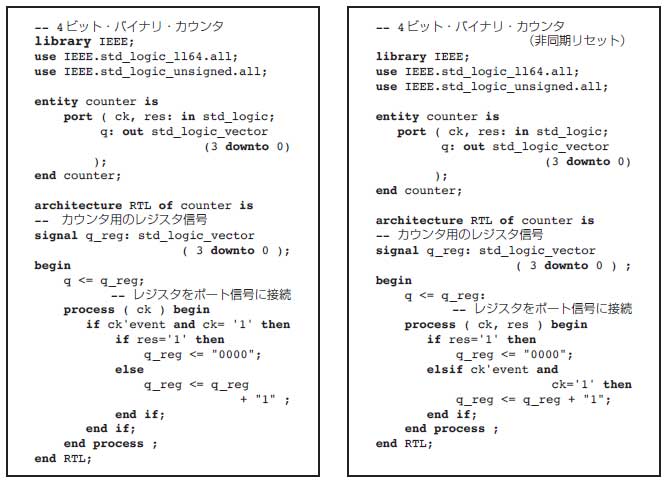

2.3 順序回路

順序回路とは,値を保持するフリップフロップやラッチを含む回路です.記述スタイルも,組み合わせ回路とは異なります.

リスト2に4ビットのバイナリ・カウンタを例に順序回路を記述してみました.リスト2(a)はクロック同期のリセット,リスト2(b)は非同期リセットです.

リスト2 実例3 ―― 順序回路

(a) 記述例(同期リセット) (b) 記述例(非同期リセット) |

順序回路もプロセス文を使って記述します.センシティビティ・リスト(processのカッコの中に記述する信号リスト)には,同期タイプはクロックのみ,非同期タイプはクロックと非同期制御信号(この場合,非同期リセットのres)を記述します.

● if文でクロック判別

if文は2方向の分岐です.if直後の条件式を評価し,

真: then以降

偽: elseがあればelse以降

を実行します.

予約語eventはアトリビュート(属性)と呼びます.信号や変数,定数などに付加されている一種のデータです.eventアトリビュートは,信号の変化の有無を意味します.つまり,

ck'event and ck='1'

は,「ckに変化があり,かつ1のとき」,つまりckの立ち上がりを意味します.したがって,同期リセットの例(リスト2(a))では,すべての動作はクロックの立ち上がりで行われます.

一方,非同期リセットの例(リスト2(b))では,クロックの有無をチェックする前に,リセット信号の判別があります.したがって,クロックに関係なく(クロックに非同期に)リセットが有効になります.

ここで用いているels ifも予約語です.else ifと記述した場合と同じ意味です.

● 内部参照のため信号宣言

VHDLは,出力ポート信号を内部で参照できないという制約があります.したがって,

q_reg <= q_reg + "1";

のように,内部で参照し,演算する記述がある場合,出力ポート信号を使うことができません.つまり,ここでは,

q <= q + "1";

と記述すると,文法エラーです.

そこで内部参照用に内部信号を用います.信号の宣言には,signalを使います.

signal:<信号名> <型>;

の形式で宣言します.

signal:<信号名> <型>:=<式>;

とすれば,初期値も与えられます(論理合成では無視されるが...).

● もう一つの記述スタイル

順序回路の記述には,もう一つの方法として,

process begin

wait until ck'event and ck='1';

if res='1' then

q_reg <= "0000";

else

q_reg <= q_reg + "1";

end if;

end process;

のようなスタイルもあります.

センシティビティ・リストのないprocess文は無限ループになります.

wait untilにより,クロックの立ち上がりを待ち,if文以下の処理を行います.この方法も論理合成可能ですが,非同期リセットなどの記述ができないため,一般的にリスト2の記述スタイルを使います.

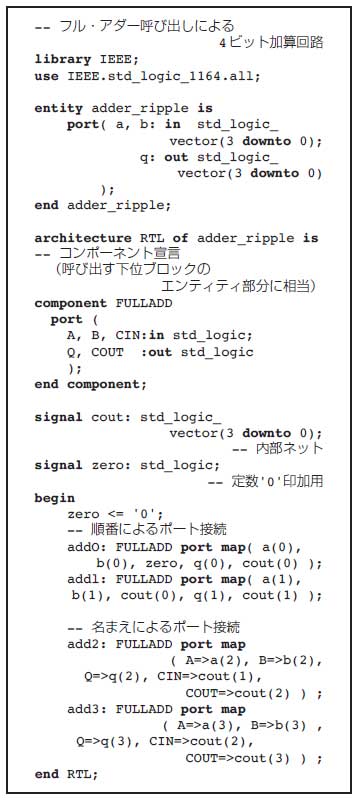

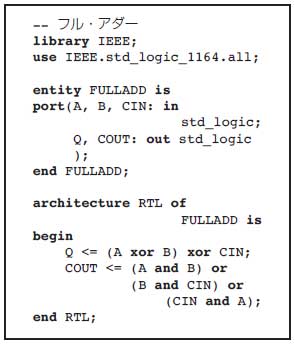

2.4 下位ブロック呼び出し

下位のブロックを接続する記述スタイルを解説します.ここでは,4個のフル・アダーを並べた4ビットのリップル・キャリ加算回路を例にしました(図5).

|

|

|

図5 下位ブロックの呼び出し

アーキテクチャ内で,呼び出すブロックのポート部分をあらかじめコンポーネント宣言により明示しておきます.アーキテクチャ内で呼び出しているブロックすべてです.ここでは1種類のフル・アダーを4回呼び出しているので,コンポーネント宣言は一つだけです.中身はエンティティと同じなのでコピー&ペーストして作成します.

下位ブロック接続時に使用する内部ネットは,すべて宣言する必要があります.アーキテクチャの宣言部分(isとbeginの間)で宣言します.coutは,フル・アダーのキャリ信号,すなわち各フル・アダー間の接続信号です.

呼び出すブロックのポートと信号の接続には2形態あります.

- 順番による接続

- 名まえによる接続

です.名まえによる接続は,

定義側ポート名 => 接続信号名

です.

接続する信号部分は,式や定数を記述することができません.したがって,フル・アダーの初段のキャリ入力(0 固定)は,内部信号zeroを宣言し,アーキテクチャ内で 0に固定しています.