初めてでも使えるVHDL文法ガイド ―― 記述スタイル編

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月27日

4.3 シミュレーション記述に役立つ各種構文

シミュレーション記述の中で,ループ構造を使う場合が多々あります.ループ構造は,プロセス文中やプロシージャ内で記述できます.

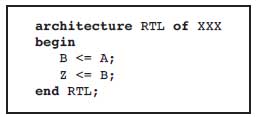

● for文

VHDLのfor文は,純粋にループを作る構文です(図12).ループ変数は,ループを回るたびに1ずつ増減します.ダウン・カウントの場合にはtoの代わりにdowntoを用います.ループ変数は,暗黙的に宣言された整数型の変数です.したがって未宣言で使用できます.また文法上,ループ変数に対して代入することはできません.

図12 for文

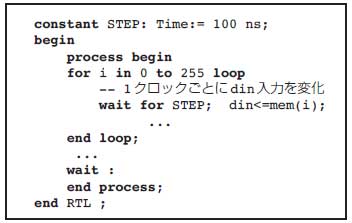

● while文

条件判断が先にくるループです(図13).whileの後の条件式が真であればloop以下を繰り返し実行します.ここでは,BUSY信号が0になるまで遅延を与え,シミュレーションを進めています.回路に対して起動信号を与え,処理の終了を待つ場合に使う手法です.処理が終了するクロック数が不明なときに有効な手段です.

図13 while文

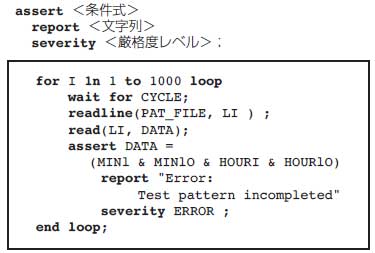

● シミュレーション結果をチェックするassert文

シミュレーション結果に応じて,メッセージを出力したりシミュレーションを中止するための構文です.図14に示した例は,あらかじめファイルに保存しておいたシミュレーションのログ・ファイルと現在の結果を比較し,不一致ならメッセージを表示してシミュレーションを中止します.RTL検証とゲート・レベル検証の比較などに有効な手法です.

図14 assert文

条件式が偽なら,report以降の文字列を出力します.厳格度レベルには,

NOTE, WARNING, FAILURE, ERROR

があります.FAILUREとERRORはシミュレーションを中止します.厳格度レベルを省略するとERRORとして扱います.

4.4 デルタ遅延

VHDLには,仮想の遅延であるデルタ遅延があります.これは,コンピュータ上のシミュレーションで,ハードウェアの並列処理を実現するために考え出された無限小の遅延です.シミュレーション時刻上は遅延量0として扱われます.

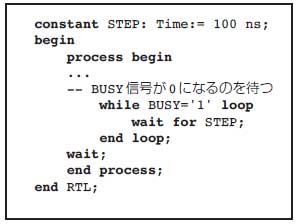

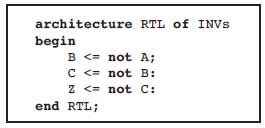

● デルタ遅延による信号の変化

図15を用いてデルタ遅延を解説します.3個の直列接続されたインバータを想定します.同時処理代入文を使って,アーキテクチャ直下に記述しました(図15(a)).

(a) 回路とVHDL記述 |

(b) 各信号のようす |

図15 デルタ遅延

入力Aが時刻Tで'1'→'0'に変化したとき,以下の順番で実行されます.

- 時刻T 代入処理 : A←'0'

- Bに代入する値の評価 : '1'

- 時刻T+Δ 代入処理 : B←'1'

- Cに代入する値の評価 : '0'

- 時刻T+2Δ 代入処理 : C←'0'

- Zに代入する値の評価 : '1'

- 時刻T+3Δ 代入処理 : Z←'1'

つまり,「評価」と「代入」を交互に行うため,代入する前に値が決まります.このため記述の順番やシミュレータに依存することなく,同一の結果が得られます.

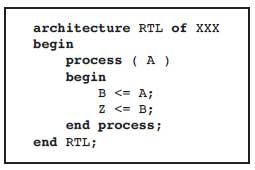

● 二つの信号代入文

信号に対する代入文には,

- アーキテクチャ直下に記述する同時処理代入文

- プロセス内で記述する順次処理代入文

があります.

いずれも記述の順番に関係なく正しく実行されますが,デルタ遅延の考えかたから,動作に若干の違いがあります.

図16では,いずれも同じ二つの代入文があります.順次処理代入文として記述されているプロセス文では,センシティビティ・リストがAだけとします.同時処理代入文は,すでに解説したように,図16(a)のように信号が変化します.

|

|

(b) 順次処理代入 |

図16 同時信号代入と順次信号代入

一方,順次処理代入文では,次のように信号が変化します.初期値を,

A='1', B='1', Z='x'

とし,時刻TでAが'1'→'0'に変化したと想定します.

- 時刻T 代入処理 : A←'0'

- Bに代入する値の評価 : '0'

- Zに代入する値の評価 : '1'

- 時刻T+Δ 代入処理 : B←'0'

- 代入処理 : Z←'1'

評価と代入が同時に行われないため,記述の順序に関係なく,BとZに正しく値が代入されます.

こばやし・まさる

参考文献

(1) Jayaram Bhasker;A VHDL Primer VHDL言語入門,CQ出版社,1995年.

(2) Douglas L. Perry;VHDL,アスキー,1996年.

(3) Z.ナバビ;VHDLの基礎,日経BP出版センター,1996年.

(4) 長谷川裕恭,VHDLによるハードウェア設計入門,CQ出版社,1995年.