初めてでも使えるVHDL文法ガイド ―― 記述スタイル編

tag: 半導体 ディジタル・デザイン

技術解説 2009年7月27日

2. RTL記述

一般に論理合成を前提とした回路記述をRTL記述と呼びます.RTLの回路記述には,次の四つの基本記述スタイルがあります.

- 簡単な組み合わせ回路

- 複雑な組み合わせ回路

- 順序回路

- 下位ブロック呼び出し

どのような回路規模であっても,この四つの記述スタイルから構成されます.

2.1 簡単な組み合わせ回路

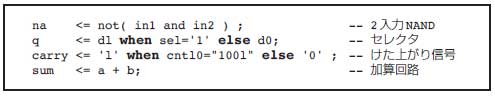

図3は,1行で記述できる組み合わせ回路です.アーキテクチャ内の同時処理代入文で記述します.それぞれの動作については,ブロック図(図3(b))を見て類推してください.

|

|

(b) 組み合わせ回路ブロック |

図3 実例1 ――簡単な組み合わせ回路

信号が多ビットか1ビットかは,宣言で決まります.したがって,セレクタや加算回路などの記述はビット数に影響されません.

図3(a)の中の重要な項目を解説します.

(1) 定数の表現

定数は,'1',"1001"のように文字や文字列として表現します.16進数や10進数の表現も可能ですが,制約が多く,実質的に2進数表記のみ用います.

(2) 論理値

1ビットの信号が取りうる値は,論理回路の世界では0と1ですが,VHDLの世界ではこれだけではありません.不定値Xや,ハイ・インピーダンスのZがあります.正確に言えば,これら論理値もパッケージの中で定義されています.

(3) 演算子

not,andなどは,論理演算子です.演算子には,文法ガイド編に示すものがあります.

(4) 代入記号

信号に対する代入には,<=を使います.ここでの代入は,アーキテクチャ直下に記述する「同時処理代入文」です.記述の順番に代入を行うのではなく,「同時」に代入されます.「接続している」と考えるとわかりやすいでしょう.

(5) 条件分岐

when ~ else を用いて,2方向分岐を記述できます.when直後の条件式が,

真: when直前の式の値を,右辺値とする

偽: else直後の式の値を,右辺値とする

となります.

when ~ elseの構造は,文法上の式ではないので,続けて演算することはできません.

q <=(d1 when sel='1' else d0)+ d2; -- エラー

などとすると,文法エラーです.

(6) コメント

--で始まり,行末までがコメントです.いちおう漢字類も使えますが,文字コードによっては文法エラーを起こすことがあります.複数行コメントはありません.

(7) 文字の大小の区別

VHDLでは予約語も含めて文字の大小を区別しません.したがって,すべて大文字で書いても,混在しても同じものとして扱います.本稿では基本的に小文字で記述しました.

2.2 複雑な組み合わせ回路

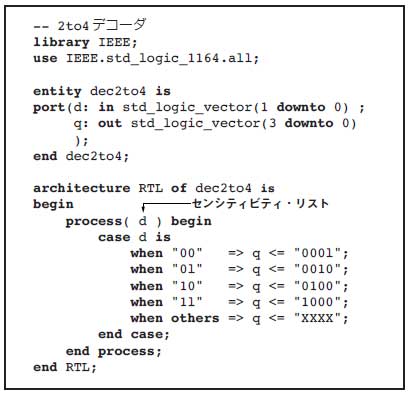

1行では表現できない複雑な組み合わせ回路は,process文を用いて記述します.図4に「2 to 4」のデコード回路を示します.完全なブロックの形式で記述してあるので,このまま論理合成可能です.

|

||

processの次のカッコの中に信号リスト(これをセンシティビティ・リストという)を記述し,これらの信号に変化があったときにプロセス内を実行します.この場合,入力dの2ビットのいずれかに変化があれば,プロセス内のcase文を実行します.組み合わせ回路をプロセス文で記述するときは,入力すべてをセンシティビティ・リストに記述します.

case文は多方向の分岐です.case文の入力dと,when直後に記述した値が一致すれば,=>以降を実行します.dは2ビットですので4方向に分岐し,出力に対する代入文を実行しています.

othersは,どれにも一致しなかった場合を指定するものです.ここでは,4通りすべてを記述してあるようですが,論理値にはX(不定値)やZ(ハイ・インピーダンス)があります.case文は,入力が取りうるすべての分岐を記述しなければならないので,実質的にothersは必須だと考えてください.