ソフトウェアで機能を定義するLSIを使ってみた ―― XMOS Semiconductor社「XS1-G」レビュー

● 割り込み処理レス

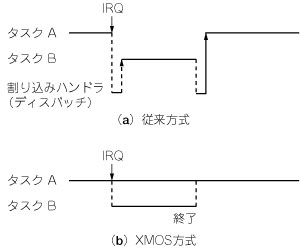

図3のように,キー入力のような遅いI/O入力など処理は,ほかの処理に影響を与えないように,割り込みで処理する必要があります.割り込みが重なって入る多重割り込みなどでは,処理の順番や受け付け禁止処理など,問題になりやすいところです.

図3 割り込み処理レス

XMOSアーキテクチャでは,これらの割り込み処理タスク自体を,それぞれのスレッドに割り当てます.一つのスレッドは,一つの入力割り込みをループで待っていればよく,ハードウェア的な割り込み処理機能を必要としません.また,割り込み処理の間はマルチスレッドにより,ほかのタスクに影響を与えることがありません.その処理だけを記述すればよいことになります.処理時間を意識した割り込みハンドラやタスクへの受け渡しなどは,考える必要がありません.

● ソフトウェアで機能を定義

FPGA(Field Programmable Gate Array)はHDL(Hardware Description Language)でハードウェア機能を定義します.ハードウェアでシステムを作るメリットは,高速に同時処理が行えるということです.

例えばUART(Universal Asynchronous Receiver-Transmitter)を考えます.通常のCPUにおいてもUARTの処理をソフトウェアで実現できます.しかし,通信中はほかの処理ができなくなってしまいます.そのため通常のマイコンなどでは,周辺回路としてUARTのポートを備えています.

XMOSアーキテクチャでは,マルチスレッドと割り込み処理レスの特徴により,UARTの機能を一つのスレッドで作ることができます.すると,通信中も待ち時間もほかの処理には影響を与えません.受信したときは,ほかのタスクに関係なく実行できます.

このように,FPGAのようなハードウェアを組むことなく,ハードウェアを模倣するソフトウェアを,スレッドに割り当てることにより,ソフトウェアだけで周辺回路を組むことができます.これが,ソフトウェア定義シリコンと呼ばれる所以です.

● 高速通信チャネル

マルチタスクの場合,タスク間が連携する必要がある場合があります.XMOSアーキテクチャでは,スレッドのメモリは同じメモリ・マップ上にあるのでデータを共有できます.また,スレッド間通信用にチャネルというものが用意されています.

チャネルは,スレッド間を1サイクルで送受信できる通信手段です.スレッドの同期などに用いることができます.また,XCore内部だけでなく,別のXCoreとも同じサイクルに通信できます.例えば,XS1-G4は四つのXCoreを持ち最大32のスレッドが実行可能です.このチャネル機能により,XCore内部同士のスレッドでも,ほかのコアのスレッドでも,相違なしにアクセスできるようになっています.

● 高速I/O

ソフトウェアでハードウェアの機能を達成するため,FPGA並みの高速なI/Oを持っています.応答時間10nsですので,I/Oでの遅延などを考えずにタイム・クリティカルな機能が構築できます.RAMなどのデータ・アクセスやスレッドごとに定義可能です.

以上,特徴を説明しましたが,これらのアーキテクチャによって,FPGAでもなくCPUでもない,OSの必要のないリアルタイム処理をソフトウェアのみで組むことができます.