LP DDR2やONFi 2.0など,メモリ・インターフェースの新規格が続々 ―― MemCon 2008

半導体メモリのコントローラ回路IPコアやシミュレーション・モデルなどの大手ベンダである米国Denali Software社は,半導体メモリの技術と製品などに関する講演会「MemCon(メムコン) 2008」を7月22日~24日に米国カリフォルニア州Santa ClaraのHyat Regency Santa Claraで開催した(写真1).

[写真1] Hyat Regency Santa Claraの外観 ※写真をクリックすると拡大できます

MemCon 2008では,半導体メモリの進化する方向が高速化,大容量化,低消費化,そして低コスト化であり,従来と変わらないことがうかがえた.また,半導体メモリの進化する方向に対応した,さまざまな入出力インターフェース規格が誕生している.

かつては,半導体デバイスの標準規格といえば,業界団体のJEDECが審議し,策定した規格のことだった.しかし現在では,半導体ベンダが独自にパートナ企業と組んで規格策定団体を立ち上げて規格仕様を策定し,団体への参加企業を募る方式がごく普通になってきた.もちろんJEDECによる標準規格の作成は続けられており,規格仕様によっては特定の規格策定団体とJEDECが連携するようになっている.MemCon 2008ではこういった動きの一端も披露された.

●低消費電力メモリの次期インターフェース

それでは,半導体メモリの入出力インターフェース規格に関連する講演を紹介していこう.Denali Software社は,低消費電力メモリ用の次期インターフェース「LP DDR2(Low Power DDR2)」の概要を解説した.講演者は,同社でTechnical Marketing Managerを務めるMarc Greenbarg氏である(写真2).

[写真2] Denali Software社のTechnical Marketing Managerを務めるMarc Greenbarg氏

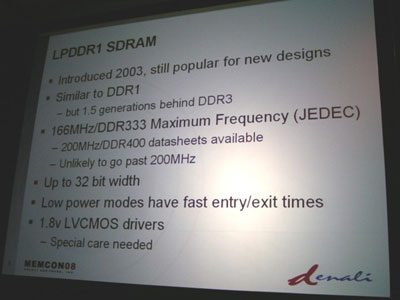

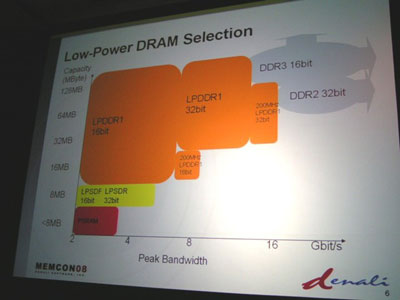

Greenbarg氏はまず,既存の低消費電力メモリ用インターフェース「LP DDR(LP DDR1)」の概要を説明した(写真3).LP DDR1は,DDRインターフェースを基本に電源電圧を1.8Vに引き下げた入出力インターフェースである.JEDECが2003年に策定した標準規格であり,最大166MHzの動作周波数(データ転送速度は333Mbps)をサポートする.データ・バス幅は最大32ビットである.

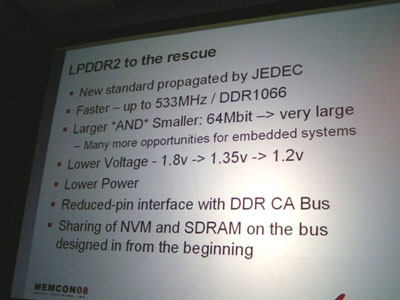

LP DDR1は「Mobile RAM」の名称で,低消費電力版DRAMに普及した.しかし最近ではデータ転送速度の低さが目立つようになってきた.そこでデータ転送速度を高めるとともに,低い消費電力を維持したメモリ・インターフェース規格「LP DDR2」をJEDECが策定した(写真4).LP DDR2では動作周波数を最大533MHz(データ転送速度は1066Mbps)に高めるともに,電源電圧をさらに引き下げている.電源電圧には1.35V版と1.2V版がある.昨年(2007年)10月には早くも,DRAMベンダのエルピーダメモリがLP DDR2準拠の512MビットDRAMの開発を発表した.

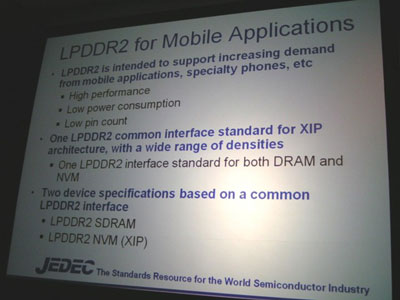

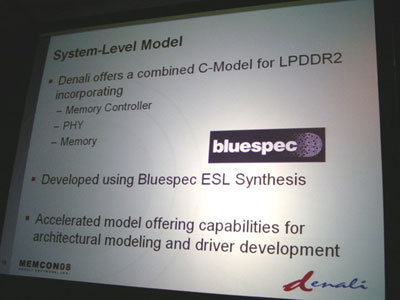

Greenbarg氏の講演スライドによると,LP DDR2はLP DDR1を完全に置き換えていくメモリ・インターフェースとなる(写真5,写真6).また,LP DDR2はDRAMだけでなく不揮発性メモリと共通のインターフェース仕様を想定しており,LP DDR2準拠のコントローラは,DRAMとフラッシュROMの両方に対応する.Denali Software社ではLP DDR2準拠のコントローラ回路やPHY回路などのモデルを提供していくとアピールしていた(写真7).

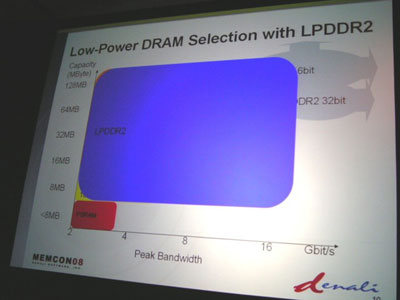

[写真5] 既存の低消費電力版DRAMの記憶容量とデータ転送速度

[写真6] LP DDR2のメモリが今後カバーする記憶容量とデータ転送速度

LP DDR1のカバー範囲をほぼすべて,LP DDR2で置き換える.

[写真7] Denali Software社はLP DDR2対応のメモリ・コントローラやPHYなどの高位モデルを供給

●JEDECではDDR3の低消費版を策定へ

LP DDR2を策定したJEDECからは,半導体メモリに関する最近の規格策定状況が紹介された.講演者は,Samsung Electronics社でDirector of Technology Enablingを務めるMian Quddus氏である(写真8).

[写真8] Samsung Electronics社でDirector of Technology Enablingを務めるMian Quddus氏

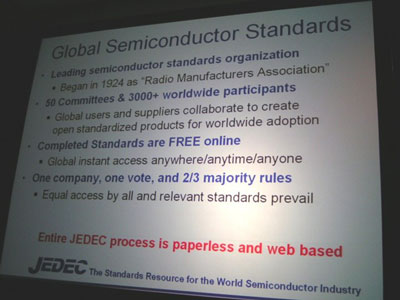

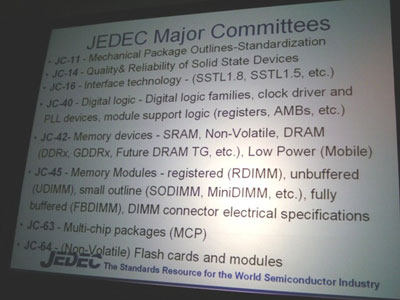

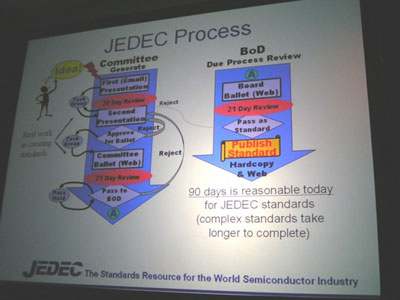

JEDECでは,JC-11からJC-64までの八つの作業グループ(Committee)が半導体メモリに関連しており,メモリ単体だけではなく,メモリ・モジュールやマルチチップ・パッケージ(MCP),SSD(Solid State Drive)などのメモリ応用品の標準規格策定を手掛けている(写真9).JEDECそのものは1924年に発足したラジオ受信機メーカの業界団体に端を発しており,現在では3,000名を超えるメンバがおよそ50の作業グループで働いている(写真10).投票は1社1票であり,投票総数の3分の2以上の賛成によって可決される.標準規格の提案から審議,意見表明のプロセスはインターネット技術を活用したWebベースで進んでおり,完全なペーパレスが実現されている(写真11).

[写真9] JEDECの半導体メモリに関連する主な作業グループ

[写真11] JEDECにおける標準規格の策定プロセス

投稿や審議,意見表明などはすべてWebベースで進行しており,ペーパレスを実現している.

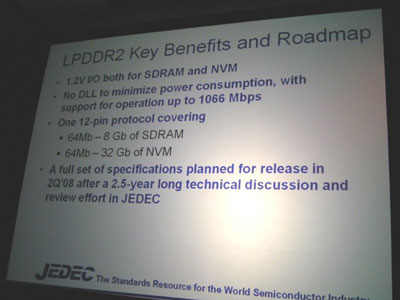

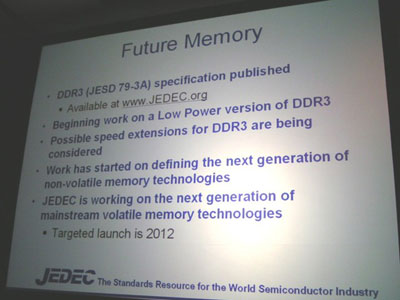

Quddus氏の講演でも,LP DDR2インターフェースの策定を最近のトピックスとして紹介していた(写真12,写真13).12ピンのプロトコルで,DRAMでは64Mビット~8Gビットの記憶容量を,不揮発性メモリでは64Mビット~32Gビットの記憶容量をサポートする.さらにDDR3インターフェースの低消費電力版規格の策定を始めたこと,次世代フラッシュROMの標準規格作成を開始したこと,次世代揮発性メモリ(DRAM/SRAM)の標準規格を策定中であることなどを報告した(写真14).

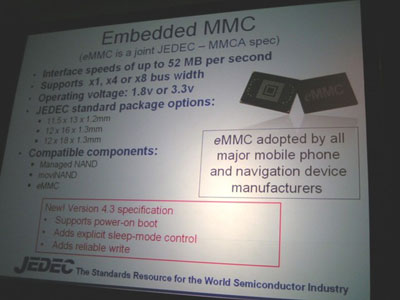

また最近では,ほかの標準規格策定団体と共同で策定作業にあたることが珍しくなくなってきた.実例として,小型NANDフラッシュ・メモリ・カードの規格策定団体である「MMCA(MultiMediaCard Association)」との共同作業を挙げていた.MMCAが策定した「MMC」インターフェースに準拠した組み込み用半導体パッケージ「Embedded MMC」の規格仕様を共同で策定した(写真15).MMCは本来,外部スロットに差し込むカード・タイプのメモリ・デバイスである.その電気的仕様を流用したフラッシュROMを,組み込み機器のメイン・ボードに搭載するための規格が「Embedded MMC」である.MMCのコントローラLSIを,メイン・ボードのメモリと外部スロットのメモリの両方に使えるようになる.

●NANDフラッシュの共通インターフェース

NANDフラッシュROMでは,共通の入出力インターフェースを策定する業界団体「ONFi(Open NAND Flash Interface Workgroup)」が2006年5月に設立され,活動を続けている.設立メンバ企業は韓国Hynix Semiconductor社,米国Intel社,米国Micron Technology社,台湾Phison Electronics社,およびソニーである.MemCon 2008ではONFiの最新の活動状況が紹介された.講演者は,Intel社でPrincipal Engineerを務めるAmber Huffman氏である(写真16).Huffman氏によるとONFiの参加企業は順調に増えており,現在は80社を超える企業がメンバとなっている.

[写真16] Intel社でPrincipal Engineerを務めるAmber Huffman氏

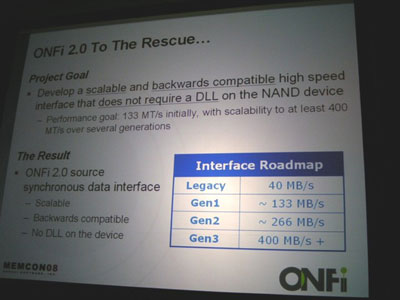

規格策定作業では,NANDフラッシュROM用高速インターフェース仕様「ONFi 2.0」を2008年2月にリリースしたばかりである.ONFi 2.0はクロック同期式のDDRインターフェースを採用しており,第1世代(Gen 1)は最大133Mbpsのデータ転送速度を有する(写真17).フラッシュROMのパッケージは従来普及してきたTSOPではなく,BGAを推奨する.また2008年5月には,JEDECと共同で規格を策定していくことで合意した.

[写真17] ONFi 2.0の基本的な考え方とロードマップ

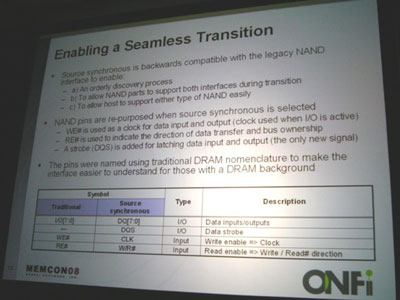

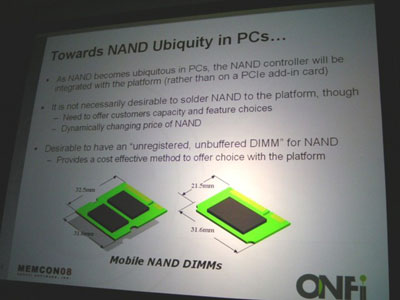

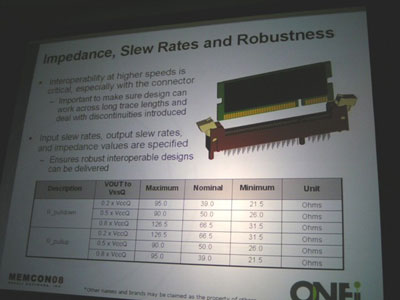

ONFi 2.0では,フラッシュ・メモリ・カードの物理的な仕様とコネクタの仕様も定められた(写真18,写真19).シミュレーションでは,目標である133Mbpsを超え,166Mbpsの信号波形がきれいに得られるという良好な結果を得ている(写真20).

[写真18] ONFi 2.0準拠NANDフラッシュROMのピン記号は,DRAMの記号を踏襲した

[写真19] ONFi 2.0準拠NANDフラッシュ・メモリ・カードの物理的な仕様

[写真20] ONFi 2.0準拠NANDフラッシュ・メモリ・カード用コネクタの概要

ふくだ・あきら

テクニカルライター/アナリスト

http://d.hatena.ne.jp/affiliate_with/