MATLABなどのシステム・レベル・ツールやマルチコア関連のデモに注目集まる ―― 45th Design Automation Conference

米国カリフォルニア州AnaheimのAnaheim Convension Centerで,2008年6月8日~6月13日に,LSI設計支援技術に関する世界最大の国際学会/展示会「45th Design Automation Conference(DAC)」が開催された(写真1).今年で45回目を迎えるDACでは,三つのキーノート・スピーチや技術講演のほか,EDA(Electronic Design Automation)に関連するワークショップなどが開催された.

本イベントではさまざまなシステム・レベルの設計ツールや,マルチコア開発環境,45nmや32nmなどの最先端プロセスのLSIを開発する際に必要となるレイアウト設計/DFM(Design for Manufacturability;製造容易性)ツールなどに関する展示が行われた.

[写真1] DACの会場となったAnaheim Convension Center

●MATLABなどからRTL記述を生成し,FPGAに実装するデモが続々

キーノート・スピーチでは米国MathWorks社のCEOであるJack Little氏が,「Idea to Implementation:A Different Perspective on System Design」というテーマで講演した(写真2).

開発するシステムが複雑になるにつれて,ドキュメント作成,設計,実装,検証の各フェーズで分業する従来のスタイルでは,設計品質が保てなくなってきた.例えば,欧州宇宙機関(ESA:European Space Agency)のロケットであるアリアン5の1号機が約40秒で爆発した原因は,単純なinteger型のオーバフローだったという.

そこで,モデル・ベース設計(MBD:Model Based Design)が重要になってきた.モデル・ベース設計では,基本となるシステムのビヘイビア・モデルを基に設計・検証を行う.モデルの正しさを検証した後に,実際の信号処理のプログラム・コードなどに落とし込んでいく.プログラム・コードの生成は自動で行う.例えばデンソーでは,コーディングに要する時間が減り,手入力に起因するエラーなどが低減したという.

LSI設計でも同じようなことがいえ,ビヘイビア・モデルからHDL(Hardware Description Language)を自動生成し,検証していくフローが必要であるという.同社は現在,MATLABで作成したビヘイビア・モデルからHDL記述やC記述を生成し,他のベンダのシミュレータなどと連携する機能を強化している.これにより,手作業によるコーディングの割合を減らし,基となる数学モデルをシステムの設計に反映し,実装・検証フローの改善を目指すという.

[写真2] キーノート・スピーチを行うMathWorks社CEOのJack Little氏

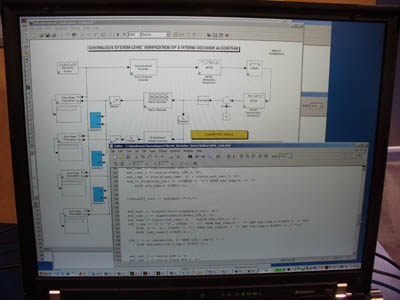

MathWorks社は,展示会場にて,同社のSimulinkからFPGAやASIC向けのHDL記述を生成する「Simulink HDL Coder 1.3」や,同じくDSPやCPU向けのC記述を生成する「Real-Time Workshop Embedded Coder 5.1」のデモンストレーションを行った(写真3).両ソフトウェアとも従来から提供されていたが,今回,機能や対応するライブラリが増えたという.

例えばSimulink HDL Coder v1.3は,複数のゲーテッド・クロック回路を使用したり,固定小数点数が扱えるようになったり,回路をパイプライン化できるようになったりした.米国Cadence Design Systems社の「Incisive」,米国Mentor Graphics社の「ModelSim」,米国Synopsys社の「Discovery Verification Platform」などの検証環境やシミュレータなどと組み合わせてコシミュレーションできるという.

[写真3] Simulink HDL Corder 1.3のデモンストレーション

Synopsys社のSymplicityグループは,MathWorks社のSimulinkからRTL記述を生成できるソフトウェア「SymplifyDSP」を利用したデモンストレーションを行った(写真4).SymplifyDSPは,ターゲットのデバイス構造やパイプラインのタイミングなどを考慮してFPGAやASICのRTL記述を生成できるという.展示会場では,Simulinkで作成したディジタル・テレビの16QAM(Quadrature Amplitude Moduration)変復調やビタビ・エラー訂正などの信号処理モデルからRTL記述を生成し,米国Xilinx社のFPGA「Virtex-5 LX330」に実装して動作させていた.

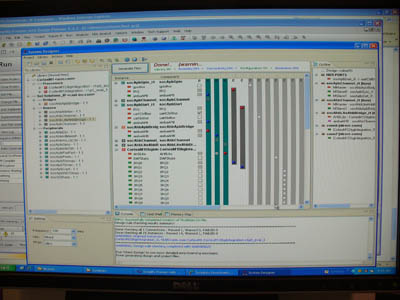

またSynopsys社のSymplicityグループは,FPGA開発環境「Symplify Premier」上でIP(Intellectual Property)コア同士を接続する機能「System Designer」を用いて,Virtex-5 LX330に英国ARM社のCortex-M1コアを実装するデモンストレーションも行っていた(写真5).

[写真4] ディジタル・テレビ向けの16QAM変復調などをFPGAに実装したデモンストレーションの様子

[写真5] System DesignerとIPコアを用いたシステム設計の様子

米国Synfora社は,C記述からFPGAのデバイス構造に適したRTL記述を生成できるソフトウェア「PICO Extreme FPGA」を展示した.Synfora社は従来,C言語からASIC向けのRTL記述を生成できる「PICO Express」と「PICO Extreme」,およびFPGA向けのRTL記述を生成できる「PICO Express FPGA」を提供していた.PICO Extreme FPGAは,PICO Express FPGAの機能強化版である.階層構造に対応したり,ブロックごとにクロックを設定したりできる.展示会場では,1080pのハイビジョン映像のエッジ検出処理をXilinx社のSpartanファミリのFPGAを使ってリアルタイムに行うデモンストレーションを実施した(写真6,写真7).FPGAは156MHzのクロックで動作させた.

[写真6] 動画のエッジ検出を行うデモンストレーションの様子

左側がエッジ検出結果,右側がオリジナルの画面.

[写真7] 実装したFPGAボードの外観

中央のデバイスがSpartanファミリのFPGA.

米国Atrenta社は,IPコアを組み合わせてSoCなどのシステム・アーキテクチャを設計する開発環境「1Team-Genesys」を発表した(写真8).同社は従来,RTL設計の段階で,タイミングや消費電力,DFT(Design for Testability)などの特性を見積もれるソフトウェア「SpyGrass」を提供していた.1Team-Genesysはその前段で利用するソフトウェアで,SpyGrassを使って設計したRTL記述や,IP-XACTに準拠したIPコアなどを用いてシステム・アーキテクチャを定義できるという.

また,SpyGrassの利用経験に基づいた最適なRTL設計のためのメソドロジ(開発方法論)「GuideWare Methodologies」を発表した.今後,同社は1Team-Genesysの利用経験も踏まえて,システム設計のメソドロジへと発展させていく予定.

[写真8] Atrenta社のブースの様子

●FPGAにも使えるColdFireコアを提供

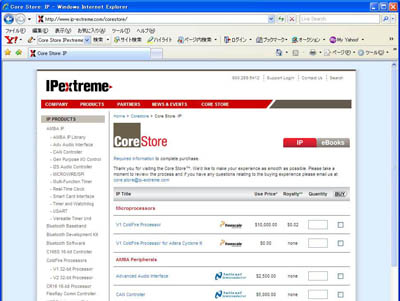

半導体ベンダのIPコアを販売する米国IPextreme社は,米国Freescale Semiconductor社の32ビットRISCプロセッサである「ColdFire V1」のIPコアの提供を開始した.ColdFireのアーキテクチャはV1からV5まであるが,今回はそのうちフットプリントの小さいV1アーキテクチャのIPコアの提供を開始した.同社は,米国Altera社のFPGA「Cyclone III」向けに本IPコアを無償で提供する予定.必要なLE(ロジック・エレメント)数は5Kていどで,ARM社のCortex-M1コアと同程度という.

IPextreme社はこのほかにも,米国National Semiconductor社やドイツInfineon Technologies社などの車載向けコントローラIPコア,インターフェースIPコア,米国Cypress Semiconductor社のUSBハブ用IPコア,米国Motorola社のクロック・ジェネレータ用IPコアなどを提供しているという.これらのIPコアは,「Core Store」と呼ばれるIPextreme社のWebサイトから入手できる(写真9).

[写真9] IPextreme社のIPコア販売サイト「Core Store」

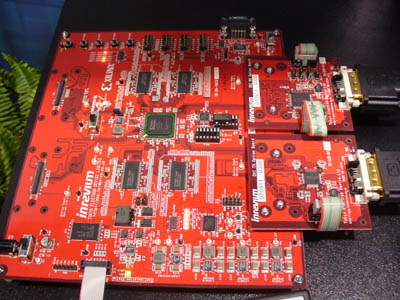

IPコア・ベンダである米国CAST社は,ARM社のFPGA向けプロセッサ・コア「Cortex-M1」をXilinx社のFPGA「Virtex-5 LX110」に実装して,H.264のエンコードを行うデモンストレーションを示した(写真10,写真11).CAST社はCortex-M1コアのほかに,AMBAバスのIPコアを紹介したり,米国Actel社のFPGA「ProASIC3」にARM7コアを搭載した評価ボードなどを展示したりした.

CAST社のIPコアは,同社のWebサイトから購入できる.また,同社はSynopsys社のSymplicityグループが「Symplify」向けに始めたIPコア提供プログラム「ReadyIP」にも参加しており,そのダウンロード・サイトからも購入できるという.

[写真10] Cortex-M1を用いたH.264エンコードのデモンストレーションの様子

[写真11] デモンストレーションで使用したVirtex-5 LXT110搭載ボードの外観