コネクタ&FPC トラブル・シューティング 11連発(2) ――同軸ケーブルを通したパルスの立ち上がり波形がなまる

ここでは,コネクタやフレキシブル・プリント基板(FPC)などにかかわる11項目のトラブル対策事例を紹介する.今回その第2回目である. (編集部)

症状

ある波形の立ち上がり時間を測定する場合,その波形の立ち上がり時間よりも10倍程度早い立ち上がり時間を持つ測定器を使えば,ほぼ正確に観測できるはずです.ところが,実際の波形の立ち上がり時間が期待される値になりません.

● 原因究明の過程

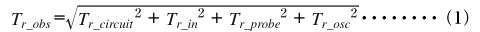

オシロスコープで観測した波形の立ち上がり時間Tr_obsは,被測定回路の立ち上がり時間Tr_circuit,入力パルス Tr_in,プローブTr_probe,オシロスコープTr_oscそれぞれの立ち上がり時間の2乗平均となり,式(1)で計算できます注1.

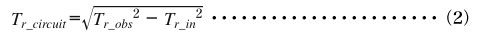

ここで,使用するサンプリング・オシロスコープは十分に高速で,かつプローブは使用していません.つまり,被測定回路の立ち上がり時間は,次式により求めることができます.

この式から,被測定回路の立ち上がり時間を得るには,入力パルスの立ち上がり時間を知ればよいと考えました.

パルス発生器の出力パルスを観測したところ,Tr_in=200ps~300psでした.そのとき,近くにいた先輩エンジニアがオシロスコープの管面をのぞき込んで,「このパルス・ジェネレータって,100ps以下の立ち上がり時間なんだけどな?」と言いました.

思い当たるのは,観測に使用したケーブルです.パルス信号の周波数が100MHz程度だからという理由で,適当な1.5D-2Vのケーブルを使っていたのです.

注1;最近のディジタル・オシロスコープでは,ブリック・ウォール・ライクなディジタル・フィルタを使用しているものが多いため,この式が成り立たないこともある.しかし,立ち上がり時間の概略値を計算する目的には十分に使える.