FPGA環境との連携が進むPCB設計環境 ――JPCA Show 2004

2004年6月2日~4日に,東京ビッグサイト(東京都江東区)にて,プリント基板に関する展示会「JPCA Show 2004」が開催された(写真1).FPGA(field programmable gate array)とプリント基板の協調設計環境や,プリント基板の同時並行(コンカレント)設計を想定した開発環境などの展示,およびデモンストレーションが行われた.

[写真1] JPCA Show 2004

2004年6月2日~4日に,東京ビッグサイト(東京都江東区)にて,プリント基板に関する展示会「JPCA Show 2004」が開催された.

●ProtelがFPGAとPCBの協調設計機能を強化

アルティウムジャパンは,同社のプリント基板設計ツール「Protel 2004」のデモンストレーションを行った(写真2).本ツールはプリント基板設計だけでなく,FPGA/PLD用の回路図エディタやHDLシミュレータなども備えている.本ツールが対応するFPGA/PLDは,米国Altera社のCyclone,MAX3000A,MAX7000AE/B/S,Stratix,米国Xilinx社のCoolRunner2/XPLA3,Spartan-II/IIE,Vertex,Vertex-II/II Pro/Eである.

今回のデモンストレーションでは,Xilinx社のFPGA「Spartan-IIE(XC2S300E)」を例に,FPGAの回路とプリント基板の回路を組み合わせたシミュレーションを行った.本ツールを用いると,プリント基板設計のときにFPGAのピン割り当てを変更し,その結果をFPGAの回路設計に反映させるといったことができる.ピン割り当ての変更情報を取得した後,ネット・ラベルの最適化を自動的に行う.

FPGAの開発には,同社の「Nexar(FPGA,プリント基板,組み込みソフトウェアの統合開発環境)」に付属する評価ボード「NanoBoard」を利用できる.NanoBoardは,Altera社のCyclone,Stratix,Xilinx社のSpartan-IIE,Spartan-3,Vertex-IIといったFPGAに対応している(NanoBoardのサブボードとして供給される).

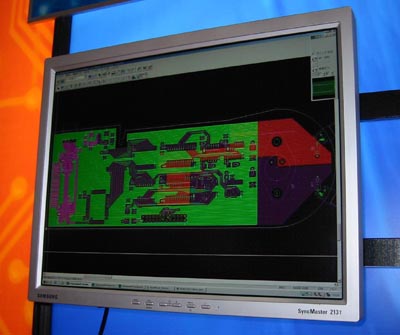

[写真2] Protel 2004のデモンストレーション

右側がプリント基板用レイアウト・ツールの画面,左側がFPGA用回路図エディタの画面.

●PADSがFPGAツールや旧Innovedar社の回路図エディタなどと統合

米国Mentor Graphics社は,同社のプリント基板設計環境「PADS」の最新版を発表した(写真3).今回のバージョン(PADS2004)では,FPGA設計に関する機能を強化した.すなわち,同社のFPGA向け設計入力ツール「DesignArchitect」やHDLシミュレータ「ModelSim」,論理合成ツール「Precision Synthesis」と統合した.さらに,米国Actel社やAltera社,Xilinx社のFPGA配置配線ツールをPADSの環境から起動したり,操作できるようにした.

さらに,回路図エディタ「DxDesigner」や部品情報データベース「DxDataBook」,アナログ設計ツール「DxAnalog」なども統合した.これらは,Mentor社が2002年に買収した旧Innoveda社の製品群である.DxDesignerには,ネット情報をスプレッド・シートから入力できる機能を追加した.最近では1,000ピンを超えるLSIが登場しており,ネット情報を回路図上で定義するよりも,スプレッド・シートから入力したほうが効率が良いという.さらに,シンボルの整列機能やストロークによるコマンド入力機能も改善した.

なお,同社はまもなく,漢字コードに対応した新バージョン「PADS2004.1J」を発表する予定.

[写真3] PADSのデモンストレーション

60mm×160mmの基板を設計しているようす.赤色は12V電圧,紫色は5V電圧,緑色はグラウンドを表している.稼働していたのは,残念ながら発表されたばかりの「PADS2004」ではなく,以前のバージョンだった.

●プリント基板の同時並行設計や分担設計を想定した開発環境

ワイ・ディ・シーのブースでは,一つのプリント基板設計プロジェクトにおいて,同時に5人のユーザが設計変更などを行える環境「εC3 Design(イプシロン・シー・キューブ・デザイン)」のデモンストレーションが行われた(写真4).デモンストレーションでは,2台のクライアントが,サーバに置かれた同一のプリント基板情報を参照し,変更を加えていた.

例えば,プリント基板上の部品を移動させるとき,だれかがある部品を選択するとその部品はロックされ(赤色表示),別の人は選択できなくなる.パターン配線についても同様.データをサーバから取得する必要があるため,ネットワークに接続して参照を開始するまでにやや時間がかかる(待ち時間はデータの容量に依存する).しかし,一度,データを取得すれば,その後の設計変更はほぼリアルタイムに行える.

本システムは2004年3月から出荷を開始している.同社のプリント基板設計ツール「CADVANCE α/αII」のユーザ企業約10社にすでに採用されているという.なお,同社のツール以外にも,米国Cadence Design Systems社のプリント基板設計ツール「Allegro」や自動配線ツール「SPECCTRA」,図研のプリント基板設計ツール「CR-5000 Board Designer」などとの間でデータをやり取りできる.

[写真4] εC3 Designのデモンストレーション

2人が同時に同じプリント基板データの修正を行うというデモンストレーション.片方があるパターンを選択すると,その部分が赤色で表示され,別の設計者は選択できなくなる.

●3次元表示を見ながらプリント基板を設計

CSiは,プリント基板設計ツール「CSiEDA」のデモンストレーションを行った.本ツールの特徴は,レイアウト(基板や部品,配線の2次元表示)に連動してプリント基板の3次元モデルが表示される点である.完成品の組み立て図なども容易に作成できるという(写真5).現在のところ,3次元表示は片面/両面基板にしか対応していないが,近々に多層基板にも対応させる予定.

また,本ツールの図形作成機能を利用して,複雑な形状のパッドを作成するデモンストレーションを行った.

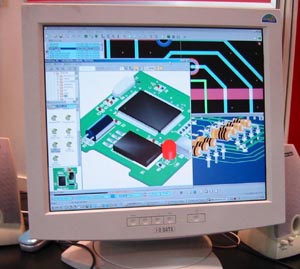

[写真5] CSiEDAのデモンストレーション

部品を移動させたり,配線を変えると,3次元モデルもそれに連動して変化する.

●光の反射率で欠陥を検出する多層ビルドアップ基板対応外観検査装置

日本オルボテックは,パッケージ/プリント基板の外観検査装置「InFinex-2100」のデモンストレーションを行った(写真6).本装置は,35μm~125μmの線幅/線間の検査に対応している.ディジタル・カメラや携帯電話で用いられているビルドアップ多層基板の外観検査に適しているという.

本装置は,光を基板に照射し,その反射率を測ることで,基板の短絡/開放,欠けなどの欠陥を見つけたり,最小線幅/線間やクリアランスの確認を行える.解像度は線幅の1/10であるため,線幅によって検査速度が異なる.線幅を125μmの場合,1時間当たり195面の基板を検査できる.また,線幅が50μmの場合は75面の基板を検査できる(いずれも,基板のサイズは475mm×610mm).検査可能な基板サイズは最大610mm×610mm,板厚は25μm~7000μm.

[写真6] InFinex-2100

InFinex-2100は2004年3月から出荷を開始している.従来のInFinex-3000シリーズと合わせた国内の出荷実績は約30台.