プロトタイピング・ボードの新製品が続々日本上陸 ――Electronic Design and Solution Fair 2004

2004年1月29日~30日,パシフィコ横浜(神奈川県横浜市)にて,設計自動化技術に関する展示会「Electronic Design and Solution (EDS) Fair 2004」が開催された(写真1).LSI設計における検証期間が増大していることを受けて,FPGAを搭載するプロトタイピング・ボード製品や論理エミュレータ製品が会場のあちらこちらで展示されていた.また,システム・レベル言語の一つである「SystemC」に関するツールのデモンストレーションも注目を集めていた.

[写真1] Electronic Design and Solution Fair 2004の会場

パシフィコ横浜(神奈川県横浜市)にて開催された.

●モジュール化されたプロトタイピング・ボードを展示

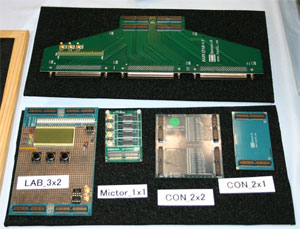

EDA商社のプロトタイピング・ジャパンは,スウェーデンのHARDI Electronics社製のプロトタイピング・ボード「HAPS(Hardi Asic Prototyping System)」を展示した(写真2).ASICのプロトタイピング(試作ボード)に必要な各種の機能を,サブボードとしてモジュール化した.米国Xilinx社のFPGA「Virtex-II(XC2V6000/8000)」を4個搭載したメイン・ボードに,あらかじめ用意されたサブボードを装着する.所望のプロトタイプを短時間で構成でき,また,サブボードをさまざまなプロジェクトで再利用できるという.

用意されているサブボードは,追加用FPGAボード,SRAMボード,SDRAMボード,FPGA間結線用ボード,ARMインターフェース・ボード,ロジック・アナライザ・インターフェース・ボード,ユニバーサル・ボード,液晶ディスプレイ/LED/スイッチ搭載ボード,DVIインターフェース・ボードなどである.また,結線用の多層フレキシブル・ケーブルやリボン同軸ケーブルも用意する.

メイン・ボードのゲート規模は800万ゲート,システム・クロックの動作周波数は100MHz~200MHz程度.I/O数は最大2,856,クロック数は最大34.

[写真2] HAPS(Hardi Asic Prototyping System)の外観

コンフィグレーション・ファイルの格納用にSmartMediaフラッシュ・メモリ・カードのインターフェースを備えている.また,コンフィグレーション用プロセッサとして,Cypress社のマイクロコントローラを搭載している.

●CPUコア内蔵FPGAを搭載するプロトタイピング・ボードも登場

EDA商社/設計サービス会社のアプリスターは,PowerPC 405コアを内蔵するFPGA「Virtex-II Pro」を搭載した米国The DuNI Group社製のプロトタイピング・ボード「DN6000K10」,「DN6000K10S」,「DN6000K10SC」の国内での販売を開始する.

DN6000K10は,USBケーブルを介してホスト・パソコンと接続するプロトタイピング・ボードである.FPGA(Virtex-II Pro 2VP70/100)を9個,DDR SDRAM(256M~1,024Mビット)を12個搭載している.各FPGAには,PowerPC 405コアが2個ずつ組み込まれている.また,PowerPCコアのコード格納用に,64Mビットのフラッシュ・メモリも搭載する.

DN6000K10SとDN6000K10SCは,いずれも32/64ビットPCI/PCI-Xバスを介してホスト・パソコンと接続するプロトタイピング・ボード.FPGAを1個実装する.DN6000K10SはVirtex-II Pro 2VP70/100/125(1,704ピンのフリップチップ・パッケージ)を,DN6000K10SCはVirtex-II Pro 2VP20/30/40/50(1,152ピンのフリップチップ・パッケージ)を搭載する.

このほか,設計教育コンサルタント会社のエッチ・ディー・ラボは,ドイツProDesign社の論理エミュレータ「CHIPit Platinum Edition」を展示した(写真3).最大1,000万ゲートの回路を実現できる.Virtex-II XC2V6000/8000を3個搭載したFPGAボードを,最大6枚まで組み込める.

[写真3] CHIPit Platinum Editionの外観

FPGA間の接続は,スイッチLSIを利用して切り替える.実際のシステム検証では,50MHzのシステム・クロックで動作した実績があるという.

●UML図からSystemCコードを生成するツールを展示

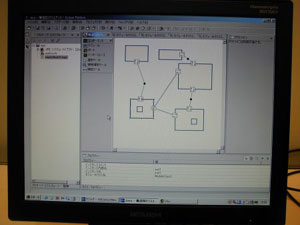

キャッツは,要求仕様を表現したUML(unified modeling language)図からSystemCコードを自動生成するツール「XModelink SoC Modeler」を展示した(写真4).本ツールは,まず,UMLのクラス図を読み込み,SystemCのアーキテクチャ構造図を生成する.次に,ユーザがモジュールやポート,インターフェースなどを入力する.これらの情報をもとに,SystemCコードを生成する.UMLのバージョンは1.4に対応している.

本ツールは,オープン・ソースのJava開発環境Eclipseのプラグインとして開発された.WindowsやLinuxの上で動作する.2004年3月にベータ版を提供し,2004年5月ごろに製品の発売を予定している.

[写真4] XModelink SoC Modelerの画面例

UML図は,IBM Rational Roseなどから読み込むことができる.

また,同社はVerilog HDLコードをSystemCコードに変換するツールのデモンストレーションも行った(写真5).変換されるコードを,行変換,列変換などのステップごとに確認できる.「Verilog HDLユーザがSystemCを習得するときの学習用にも使えるのではないか」と同社は考えている.本ツールは参考出展であり,最終的にどのような形態の製品になるかは未定だという.

[写真5] Verilog HDLコードをSystemCコードに変換するツール

最終的な製品仕様(GUIなど)は未定.

●NECエレ,V850EコアやARMコア向けシステムLSI開発環境を提供

NECエレクトロニクスは,システムLSI用の開発環境「MICROSSP」を展示した.同社のCPUコアである「V850E1/2」や「ARM946E」と各種IPコアを組み合わせたシステムLSIの開発環境やテストベンチなどを提供する.

同社は,USBやPCIといったインターフェースやメモリ,タイマなどの周辺IPコアを顧客に提供している.MICROSSPでは,コア単体ではなく,CPUとその周辺IPコアをバス接続(ARMの場合はAHBとAPB,V850Eの場合はVSBとNPB)した形で提供する.搭載されるIPコアは,顧客の要求に応じてカスタマイズ可能.ただし,カスタマイズの作業は同社が行う.

シミュレーションについては,RTL(register transfer level)のHDLモデルとサイクル精度のSystemCモデルの両方を用意する.モデル作成には,米国Synopsys社の「CoreAssembler」を利用するが,MICROSSP用のIPコア・ライブラリやSystemCモデル生成機能などは,NECエレクトロニクスから提供される.RTLモデルはすでに提供を行っている.SystemCモデルは開発中であり,2004年前半には提供を始める予定.

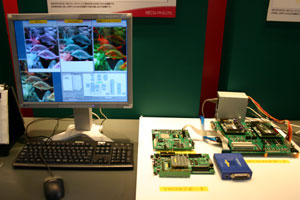

さらに同社は,実動作検証用に評価ボードを用意する(写真6).現在は,使用するCPUコア(ARM946E,V850E1,V850E2)ごとに評価ボードが異なる.ARM946Eコア用評価ボードには,PCIやUSB,Ethernetなどのインターフェースを備えた拡張ボード用スロットが付いている.CPUコア部については,英国ARM社の開発ボード「Integratorコアモジュール」を別途購入して接続する必要がある.2004年3月にはV850E1,V850E2の両方に対応した評価ボードを提供する.また,同年後半には,さらにARM946Eにも対応した評価ボードを出荷したいという.

[写真6] MICROSSPの評価ボード

ARM用,V850E1(動作周波数100MHz)用,V850E2(同200MHz)用の3種類を用意する.ARMコアについては,英国ARM社の開発ボード「Integratorコアモジュール」が別途必要になる.