プロトタイピング・ボードの新製品が続々日本上陸 ――Electronic Design and Solution Fair 2004

●アイピーフレックス,動的再構成可能プロセッサの第2世代を紹介

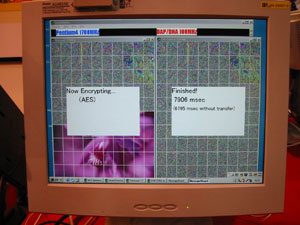

アイピーフレックスは,ダイナミック・リコンフィギャラブル(動的再構成可能な)プロセッサ「DAP/DNA-HP」のデモンストレーションを行った(写真7).本プロセッサは,ALU(数値演算ユニット)やメモリ,カウンタ,遅延素子といったエレメント(回路素子)の間の結線を変えることで,機能を動的に(動作中に瞬時に)変更できる.機能を随時切り替えていくことで,処理性能を引き上げたり,消費電力を削減できる.エレメント数は144,動作周波数は100MHz.例えば,医用電子機器や産業用機器などの負荷の重い画像処理に利用できる.

また,同社は本プロセッサの第2世代のチップとなる「DAP/DNA-2」を2004年2月から発売する予定.動作周波数を166MHzに上げ,エレメント数も376に増やした.DAP/DNA-HPの場合と同じように,評価ボードを用意する.

[写真7] DAP/DNA-HPのデモンストレーション

AES(advanced encryption standard)の暗号化/復号化処理を1.7GHz動作のPentium 4とDAP/DNA-HPで実行・比較した.

一方,富士通は,アイピーフレックスのダイナミック・リコンフィギャラブル・プロセッサ「DAP/DNA」をカスタマイズするサービスを開始することを明らかにした.例えば,DAP/DNAが搭載する演算器のうち,不要な部分をユーザ回路として利用するなどのカスタマイズを行う.設計上の技術支援などはユーエスシー・デジアークが担当する.本サービスの提供開始時期は未定.

●Cadence,400万ゲートを一括合成できる論理合成ツールを展示

米国Cadence Design Systems社は,200万~400万ゲートの回路を一括合成できる論理合成ツール「Encounter RTL Compiler」のデモンストレーションを行った(写真8).Encounter RTL Compilerは,同社が2003年4月に買収した米国Get2Chip社によって開発されたツールである.Cadence社はこれまで「BuildGates Systhesis」という論理合成ツールを顧客に提供してきたが,今後は全面的にRTL Compilerに移行していくという.

RTL Compilerでは,まず,面積をあまり最適化せず(例えば,駆動能力の高いセルを割り当てる),タイミング優先で回路を合成する.続いて,タイミング制約を参照しながら,タイミング違反になっているクリティカル・パスを修正していく.最後に,面積を最適化する.従来の論理合成ツールは面積を優先的に最適化する傾向にあったため,タイミングの収束に時間がかかっていたという.今回の手法により,論理合成の実行時間は増加するものの,タイミング収束のための論理合成の手戻り回数が減り,トータルの開発期間は短縮するという.また,75万~100万インスタンスを一括して扱えるようになり,事前のモジュール分割や各モジュールに対するタイミング・バジェットの作業が不要になった.

[写真8] Encounter RTL Compilerのデモンストレーション

250万ゲートの回路を約8時間で合成できたという.

●製造容易化設計の基盤データベース,デモを2004年末公開

EDAツールに関する標準化を推進している非営利団体の米国Si2(Silicon Integration Initiative)社は,半導体の設計データと製造データの両方を管理する標準データベース「OA-UDM(OpenAccess-universal data model)」のパイロット・プロトタイプ・システムを2004年末までに構築すると発表した(写真9).OA-UDMは設計工程と製造工程の橋渡しをするデータベース(および,そのデータベースにアクセスするためのAPI)である.半導体製造装置や半導体材料の業界団体であるSEMI(Semiconductor Equipment and Materials International)とSi2社が協力して標準化を行っている.Si2社がすでに策定しているEDAデータベースの共通仕様「OpenAccess」をベースに,製造用データ(マスク描画データや製造用リソグラフ・データなど)を扱えるように拡張した.

今回,Si2社(および,その下部組織であるDesign to Mask Coalition)が作成するのは,OA-UDMのメリットを実証・評価するためのデモンストレーション・システムである.OA-UDMが普及すれば,マスク作成コストを大幅に低減できるという.例えば,LSIの製造用マスクの検査工程では,設計情報をまったく考慮せずに検査が行われている.設計情報を参照しながらマスク検査を行えば,不要な検査を省略して検査時間を短縮できるという.また,欠陥が生じやすい箇所(例えば,高速信号が伝播するクリティカル・パス)の情報を設計データから抽出して,それを製造用マスクのマージンに反映させるといったことも可能になる.

このように設計と製造を連係させてLSI開発全体を最適化する手法は,「製造容易化設計(DFM:design for manufacturability)」と呼ばれている.

[写真9] OpenAccessの普及推進活動を行っているSi2社の経営陣

左がSi2社 President & CEOであるSteven E. Schulz氏,中央が同社 Vice President of TechnologyのSumit DasGupta氏,右が同社 Director of Business Development, OpenAccessのBob Carver氏.EDS Fairの開催に合わせて来日した.

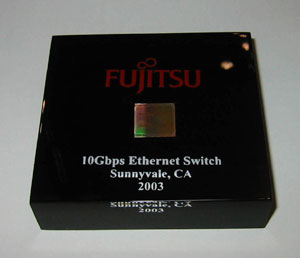

●富士通,12ポートのXAUIを内蔵する10G EthernetスイッチLSIを展示

富士通は,XAUIインターフェースに対応したI/Oを12ポート内蔵する10GビットEthernet向けスイッチLSI「MB87Q3050」を展示した(写真10).MAC(media access control)を含むレイヤ2(データリンク層)のスイッチングを行う.通信装置やサーバなどの分野における需要を見込んでいる.

本スイッチLSIの動作周波数は312.5MHz,消費電力は15W(標準値).スイッチ遅延時間は450ns(無負荷時)である.

[写真10] 富士通の10GビットEthernet向けスイッチLSI「MB87Q3050」

XAUIインターフェースに対応したI/Oを12ポート内蔵する.パッケージは782ピンのFCBGA(flip chip ball grid array).外形寸法は35mm×35mm.すでに出荷を開始している.

また,同社は本スイッチLSI用の評価ボードも展示した(写真11).9個の電気ケーブル用コネクタを備えている.InfiniBand用ケーブルを利用した場合,伝送距離は最大5m.また,信号の高周波成分を強調して伝送時の損失を補うプリエンファシスの機能を備えている.同社は,さらに電気的特性を改善し,伝送距離を延ばしたスイッチLSI製品を近日中に発表するという.

[写真11] 富士通のMB87Q3050用評価ボード

MB87Q3050のほか,米国Motorola社のマイクロプロセッサ「MPC860T」,64MバイトのSDRAM,4Mバイトのフラッシュ・メモリなどを搭載している.OSはVxWorksを使用.

●図研,RTPで動画を送信するミドルウェアを展示

図研は,動画のキャプチャと再生をリアルタイムで行うミドルウェアのデモンストレーションを行った(写真12).RTP(realtime transport protocol)とMPEG-4を利用している.RTPはリアルタイム性を重視したプロトコルで,音声伝送などによく使われている.監視カメラなどの用途における利用を想定している.

[写真12] RTPで画像を送信するミドルウェアのデモンストレーション

QCIF(176ピクセル×144ピクセル),15フレーム/sで画像を送信している.デモンストレーションではリアルタイム通信ではなく,あらかじめファイルとして取り込んだ映像を再生していた.