携帯機器向け基板,「軽・薄・短・小」に加えて高速性も実現 ――インターネプコンワールド JAPAN 2004

2004年1月28日~30日,東京ビッグサイト(東京都江東区)にて,「インターネプコンワールド JAPAN 2004」が開催された(写真1).同展示会では,「第5回 プリント配線板 EXPO」,「第5回 半導体パッケージング技術展」など,五つの技術分野の展示が行われた.小型・薄型をうたったプリント基板やパッケージ技術が続々登場する中で,高速信号伝送にも対応できるプリント基板が注目を集めていた.例えば,トッパンNECサーキットソリューションズは,コア材としてポリイミド・テープを用いることで4層基板の厚みを150μmとし,かつ4.5GHzの信号伝送に対応できる半導体パッケージ用インターポーザ(パッケージ基板)を展示した.

[写真1] インターネプコンワールド JAPAN 2004

2004年1月28日~30日,東京ビッグサイト(東京都江東区)にて,「インターネプコンワールド JAPAN 2004」が開催された.3日間の来場者数は,前年より約3,300人増えて55,971人となった.

●コアにポリイミド・テープを使い,4.5GHzの信号伝送に対応

トッパンNECサーキットソリューションズは,凸版印刷の半導体パッケージ用インターポーザ「Core-less Substrate」を採用したLSIを展示した(写真2).4.5GHzの高速信号伝送にも対応できる.インターポーザ(サブストレートとも呼ばれる)は,ベア・チップなどを実装するパッケージ基板.最近ではビルドアップ方式の多層構造を採っているものが珍しくない.

従来は,ガラス基材(FR-4など)のコア層にビルドアップ層を積み上げることが多かった.本インターポーザではコア材としてポリイミド・テープを使用することにより,基板を薄くした.また,FR-4などと比べてポリイミドは誘電正接(tanδ)が1けた小さいため,伝送損失が低減する.さらに,基板厚が薄くなったために配線長が短くなり,速度を向上させやすくなった.これにより,高速な信号伝送にも対応できるようになったという.

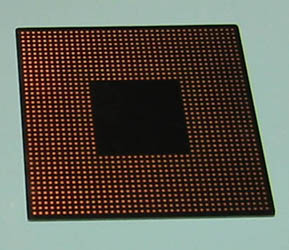

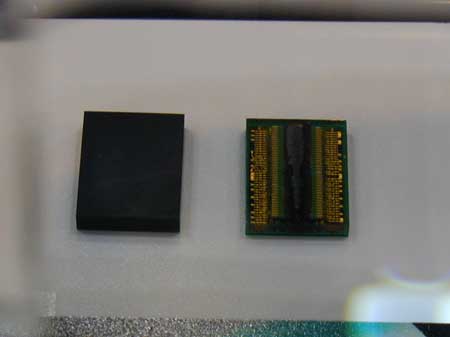

[写真2] Core-less Substrateを採用したパッケージ基板

写真は1,344ピンのFCBGA(flip chip ball grid array).外形寸法は41mm×41mm,基板厚は150μm.

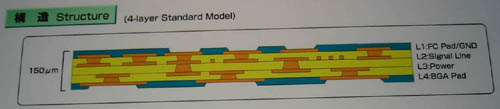

本インターポーザは4層構造で,基板の厚みは150μm(写真3).誘電率は3.3~3.4である(1MHz).線幅/線間は20μm/20μm,ビア径は40μm,ランド径は90μm(いずれも最小値).例えば,伝送距離が20mmの場合,FR-4をコア材に利用すると周波数帯域は2GHz程度である.一方,本インターポーザでは4.5GHz(透過特性S21=-1.0dB)となる.

現在は,信頼性などの評価を行っている.2005年には量産出荷を開始したいという.

[写真3] インターポーザ基板の構造

4層基板の構造.現在,Core-less Substrateの6層基板も開発している.

●3.5mm×3.2mm×1.7mmと小さいリモコン・レシーバを展示

ソニーケミカルは,外形寸法が3.5mm×3.2mm×1.7mmと小さい赤外線リモコン・レシーバ・モジュール「超小型リモコン」を展示した(写真4).フォトダイオードと復調ICが一つのパッケージに封止されている.既存のモジュールの外形寸法は4mm×5mm程度だった.

今回展示したモジュールの電源電圧は2.7~5.5V,搬送周波数は30kHz~76kHzの範囲で選択できる.動作温度は-30~+85℃.鉛フリーに対応しており,はんだ温度が255℃のリフロを実施できる.構造上の信頼性や動作保証についてはすでに確認済みだが,量産生産の時期は未定.どういったアプリケーションに利用していくかなどを,顧客といっしょに検討していきたいという.

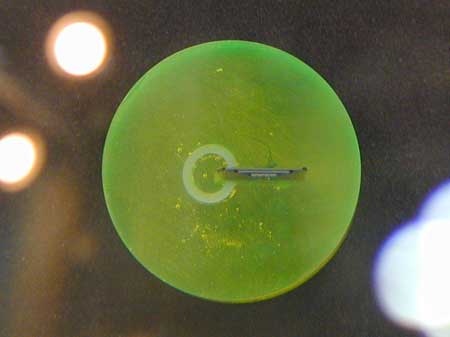

[写真4] ソニーケミカルの「超小型リモコン」

外形寸法は3.5mm×3.2mm×1.7mm.復調ICはフリップチップ実装,フォトダイオードはワイヤ・ボンディングでパッケージ内に実装されている.

このほか,同社は「中空構造パッケージ」も展示した.これは,配線パターンとソルダ・レジストの段差を利用して,基板とICチップの間に空間を作ったパッケージである(図1,写真5).従来は,SAW(surface acoustic wave;表面弾性波)フィルタやMEMS(micro electro mechanical systems)ジャイロ・センサなどは,チップの表面が直接基板に接触しないように,キャビティ構造を採っていた.キャビティ構造のパッケージの厚さは1.8mm.これに対して中空構造を利用すると1.3mmになる.携帯電話などの薄型の部品が求められる市場での利用を見込んでいる.現在は,信頼性などを評価中.

[図1] ソニーケミカルの「中空構造パッケージ」の構造

IC表面の物理的変位を妨げないように,チップと基板の間に空間を持たせている.

[写真5] ソニーケミカルの「中空構造パッケージ」

半導体メーカから提供されたセンサ・チップをソニーケミカルがパッケージに封止する.本パッケージについては,特許出願中.

●電極をチップ上に設けたスタック・パッケージを展示

イデアシステムは,三つのチップを3段に積層(スタック)したSIP(system in package)を展示した(写真6).実装方式はフリップチップ実装.積層するチップのサイズを上から順番に小さくして,それぞれを1枚のインターポーザにバンプ(電極)接続する.これにより,パッケージの外形寸法を,内蔵するもっとも大きいチップの外形寸法とほぼ同じにできる.同社はこの方法を「ミルフィーユ方式」と呼んでいる.

[写真6] 3次元フリップチップ実装の試作品

三つのチップを,1枚のインターポーザ基板上に搭載している(薄い影のように見える部分がインターポーザである).

また,同社は4個のチップを積層して厚さ3mmのパッケージに収めたSIPも展示した(写真7).携帯電話などへの搭載を視野に入れて,将来は厚さを2mm以下にしたいと考えているという.

[写真7] 4個のチップを3mm厚のパッケージに封止

256MバイトのDRAM.SiPコンソーシアム,イビテックと共同開発した.

●内層配線を利用して受動部品を形成する部品内蔵基板を試作

三菱電機は,受動部品を埋め込んだプリント基板の試作を行った.基板の内層配線を利用してインダクタ,キャパシタ,抵抗を形成した.本基板を利用することで部品点数を削減でき,組み立てコストなどを低減できる見通し.

現在は,周波数特性や部品単体の容量などの評価を行っている.現時点で作成できるキャパシタの容量はpFオーダ,インダクタンスは10nH程度である.本基板の適用分野として,RF(高周波)通信モジュールを想定している.リフロに対する温度耐性やケージ変化については,現在評価中.2年後の実用化を目標にしている.