東芝がLSIの斜め配線技術を実製品に適用へ,2004年中の生産を目ざす ――90nmプロセスでX Architectureの効果を実証

東芝は,45°方向や135°方向の斜め配線(X Architecture)を利用して民生機器向けの回路ブロックを設計した(写真1).さらに,90nmのCMOSプロセスを使用して同回路ブロックを組み込んだテスト・チップ(TEG:test element group)を製造し,斜め配線技術の有効性を確認した.すでに,半導体製造装置メーカの米国Applied Materials社が斜め配線を利用した90nmプロセスのテスト・チップを開発しているが,これは同技術を利用したチップを実際に製造できるかどうかを評価するためのチップだった.実際の回路ブロックをLSI化して機能動作を確認したのは,今回が初めて.

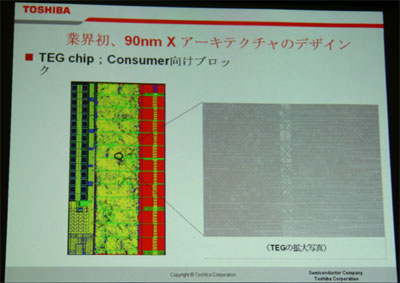

[写真1] 東芝が開発したテスト・チップの回路ブロック

回路ブロックのマスク・レイアウトを公開した.民生機器用LSI向けの回路ブロックをLSI化した.

●斜め配線のコンソーシアムに38社が参加

現在のディジタルLSIは,人手で設計される小規模なセルなどを除けば,すべて垂直・水平方向だけの配線を使ってセル間や回路ブロック間を結線している.これは,マスク・レイアウトの設計で利用されている自動配線ツールがそのような設計ルールを前提に作られているためである.垂直・水平方向の配線に加えて,45°方向や135°方向の斜め配線を利用すれば,配線長やビアの数が減少する.これによって,LSIの性能が向上したり,消費電力が少なくなるという.

2001年6月には,斜め配線技術を開発した東芝や米国Simplex Solutions社(同社はその後,米国Cadence Design Systems社に買収された)が中心となって,同技術の普及推進団体である「X Initiative」が設立されている.現在,半導体メーカやEDAベンダ,IPコア・ベンダ,半導体製造装置メーカ,マスク・メーカなど,38社がこのコンソーシアムに参加している.

●2004年には斜め配線を適用した製品が登場

今回,東芝が設計した回路ブロックの規模は30万ゲート.配線層数は5層.そのうちの第3層と第4層に斜め配線を適用した.その結果,従来の垂直・水平配線のみの場合と比べて,配線長が14%,ビア数が27%減少したという.配置配線ツールについては,斜め配線に対応したものを新規に開発して使用した.寄生容量/抵抗抽出ツールやDRC(design rule checker),LVS(layout versus schematics)などは,既存のツールに斜め配線のための機能(ライブラリなど)を追加して対応した.

同社は,2004年中に斜め配線技術を利用したLSI製品を開発する計画.「現在,適用する製品を選定中.年内に決定して2004年中に開発,できれば生産まで持っていく」(東芝 セミコンダクター社 設計技術技師長 吉森崇氏,写真2).

[写真2] 米国Cadence Design Systems社 Chief Technology Officer, New Business IncubationのAki Fujimura氏(左)と,東芝 セミコンダクター社 設計技術技師長の吉森崇氏(右)

記者発表が行われ,X Initiativeの最近の活動が紹介された.