PCI Express対応の開発環境が整いつつある ――インテル デベロッパ・フォーラム Japan Spring 2003

2003年4月9日~11日,ヒルトン東京ベイ(千葉県安浦市)にて,「インテル デベロッパ・フォーラム Spring Japan 2003」が開催された.パソコン関連や通信分野などについての基調講演や報道関係者向け説明会が開かれたほか,米国Intel 社製のCPUを搭載した製品などの展示が行われた.今回は,2002年7月にPCI-SIG(PCI Special Interest Group)によって策定されたPCI Express対応製品に焦点を当てて報告する.

●PCI Expressの物理層からトランザクション層まで測定する

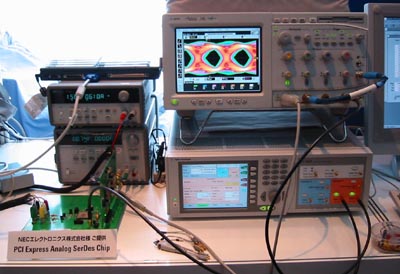

アジレント・テクノロジーのブースでは,NECのPCI ExpressインターフェースLSIのサンプル・チップを用いて,プロトコル解析やアイ・パターンの測定を行っていた.まず,同社のロジック・アナライザ「16702B」とPCI Express用パケット解析プローブ「N4220A」を組み合わせて,トランザクション層(TLP)とデータリンク層(DLLP)のパケットのデコードを行っていた(写真1).PCI Express用のプロトコル・アナライザとエクササイザ(疑似的な通信データを生成して,動作を確認する機器)も現在開発中であるという.

[写真1] PCI Expressプロトコル解析装置

ロジック・アナライザ「16702B」(写真下)とPCI Express用パケット解析プローブ「N4220A」(写真上).同ロジック・アナライザとSerial ATA用パケット解析プローブ「N4219A」を組み合わせれば,Serial ATAプロトコル解析用として利用できる.

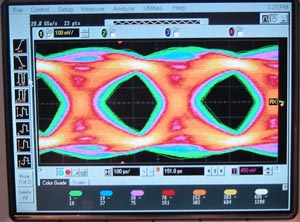

また,同ロジック・アナライザと同社のオシロスコープ「Agilent 54855A Infiniium」を用いてアイ・パターンを測定した(写真2).被測定ボードはIntel社製であり,NECのPCI Express用SerDesチップを搭載している.ここでは,2.5Gbpsのデータ転送速度で測定が行われていた.オシロスコープの設定を変更することにマスク・テストも可能.オシロスコープのプロービングには,入力抵抗が50Ωのプローブ・ヘッドを使用している.このプローブ・ヘッドは7GHzまでの帯域を保証している.ヘッドの先を測定箇所に直接はんだ付けできる.

(a) 測定環境

(b) アイ・パターン

[写真2] アイ・パターンを測定

被測定ボードはIntel社製.NECのPCI Express対応SerDesチップを搭載している.

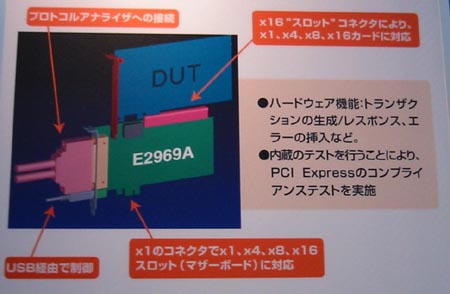

さらに,今回のIDF2003において,同社はIntel社と共同でプロトコル・テスト・カードを開発すると発表した.このテスト・カードは,被測定ボードのPCI Expressスロットに直接差し込んで使用する(写真3).テスト・カードから取得したプロトコルのデータは,プロトコル・アナライザまたはロジック・アナライザで表示する.TLPとDLLPの認証試験に利用できる.同テスト・カードにはUSBインターフェースが搭載されており,パソコンからのテスト制御はこのUSBを介して行われる.PCI-SIGからは,まだ正式に認証試験の内容は発表されていない.同社とIntel社はテスト項目の洗い出しや具体的な適合試験の方法などの検討を行い,これをPCI-SIGのほうへ提案していく方針.本テスト・カードの受注は2003年6月から開始し,同年8月から出荷を開始する予定.

[写真3] プロトコル・テスト・カードの概要

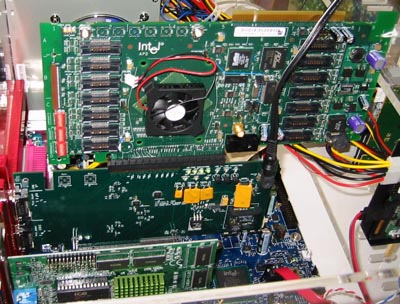

●PODを取りかえれば,あらゆるインターフェースに対応可能

米国Data Transit社は,プロトコル・アナライザ「BUS DOCTOR」を用いてデモンストレーションを行っていた(写真4).テスト用のメイン・ボード(テスト用に「Kyrene」というIntel社のチップセットを搭載)とPCI Expressの被測定ボードはIntel社製.このメイン・ボードでは×1~×16までのリンクを測定できる.今回のデモンストレーションでは×8のリンクの測定が行われていた.

(a) 測定システム(ノート・パソコンの下の青い製品が「BUS DOCTOR」,その横にある黒い製品がPCI Express用のPOD)

(b) 評価用ボード(いちばん上にあるボードが評価用ボード.その下のボードがタップ・ボード.メイン・ボードはいちばん下に見える青いボード)

[写真4] プロトコル・アナライザ「BUS DOCTOR」

今回のデモンストレーションは×8で行われた.4.6Gバイトのトレース用メモリが搭載されており,2億5千6百万のイベントを取りこめる.メモリ容量によって価格は異なる.

プロトコル・アナライザのほか,タップ・ボードとPODはData Transit社製.プロトコル・アナライザのトレース(データ取り込み)用メモリの容量は,製品によって異なる(最小512Mバイト,最大46Gバイト).今回のデモンストレーションに用いられたプロトコル・アナライザには,4.6Gバイトのメモリが搭載されていた.コマンド,パケット,Descriptをそれぞれ色を変えて表示できる.ロジック・アナライザの機能も備えている.また,それぞれの通信規格(ATA/ATAPI,USB1.1/2.0,1394a,SerialATA,Fibre Channel,ギガビットEthernet,Infinibandなど)ごとにPODを用意している.本プロトコル・アナライザは,最大8台をスタックして利用可能.OSはWindows 2000/XP.

PCI Express用のPODは,2003年4月末から出荷を開始する予定.国内販売代理店はNEC三栄.

●任意波形ジェネレータで受信側電圧をチェック

日本テクトロニクスのブースでは,同社のディジタル・オシロスコープ「TDS6604」に現在開発中のPCI Expressのアイ・パターン測定用ソフトウェアをインストールして,アイ・パターンの測定を行っていた.評価ボードは,Intel社製(NECのチップを搭載).マスク・テストも行える.

また,任意波形ジェネレータ「AWG710」を利用して,受信側の感度テストのデモンストレーションを行っていた.PCI Expressでは,送信側の電圧は差動電圧のピーク・ツー・ピークで800mV,受信側の電圧は175mVと規定されている.そのため,受信側の電圧を175mVまで下げた場合に確実に動作するかどうか,あるいはある下限電圧まで下がるときちんと停止するかどうかをチェックする必要がある.

同社は2003年中にはアイ・パターン測定用ソフトウェアを製品化する予定.

[写真5] 日本テクトロニクスのブースのようす

ここでも,PCI Expressに対応したアイ・パターンの測定は注目を集めていた.