半導体チップ識別セルやDFTテスタが登場 ――Semicon Japan2002

2002年12月4日~6日に,幕張メッセ(千葉県千葉市)において,半導体製造装置やテスト装置,半導体材料に関する展示会「セミコン・ジャパン 2002」が開催された.半導体製造の最大の課題である「歩留まり向上」をうたい文句とした展示物が目立った.例えば,個々の半導体チップにIDセルを埋め込む技術や,テスト容易化設計に特化したLSIテスタのデモンストレーションが行われた.

●半導体チップにIDを付けるサービスを開始

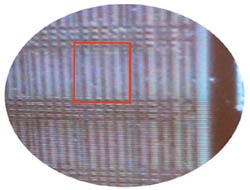

日立超LSIシステムズは,半導体チップ識別セルのデモンストレーションを行った(写真1).同技術の特許は米国SiidTech社が保有している.両社は2002年10月に半導体チップ識別用IPコアの提供やシステムの共同開発などについての提携を結んている.同時に,日立超LSIシステムズは,日本およびアジアにおける独占的なサブライセンス権を取得している.

SiidTech社が開発した半導体チップ識別技術は,一つ一つのシリコンのダイ,またはIPコアに対して電気的に読み出せるID番号を自動的に付与する技術である.IDを付けることによって個々のチップの製造履歴が特定できるため,不良品が発生した場合に故障解析を迅速に行えるようになる.このほか,RFID(非接触自動認識装置)など,セキュリティや認証などの用途でも利用できる.

本技術は,通常の半導体製造工程を利用してID番号を付けられるため,EPROMやフラッシュ・メモリにIDを書き込む方法やレーザでトリミングする方法に比べて安価である.日立超LSIシステムズは,2002年11月から半導体チップ識別用IPコアの受注を開始している.今後は,半導体チップ識別技術の認知度を上げるための活動を行い,IPコアの提供だけでなく,設計,製造,応用製品企画などを含む統合的なサービスを提供していきたいという.

(a)デモンストレーションのようす

(b)(a)の画面の拡大図[写真1] 半導体チップ識別セル

0.13μmルールで試作した半導体チップの識別セル(赤い四角の中が一つのIDセル・ブロック).

●テスト容易化設計に特化した低価格テスタを展示

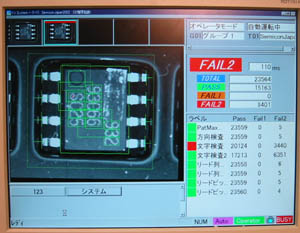

エー・テイー・イー・サービスのブースでは,米国Teseda社製のDFTテスタ「Validator 500」のデモンストレーションが行われていた(写真2).DFTテスタは,テスト容易化設計(DFT:design for testability)を前提とした安価なLSIテスタである.

本テスタは,DCスキャン検証やメモリBIST(built-in self-test),ロジックBIST,バウンダリ・スキャン(IEEE1149.1)などを適用したLSIを取り扱える.ATPG(Automatic Test Pattern Generation)として,米国Mentor Graphics社の「FastScan」と米国Synopsys社の「TetraMAX」に対応している.テスト・データ形式はSTIL(IEEE 1450-1999),I/O数は300ピン.そのほか,16ピンのクロックと16ピンのスキャン・イネーブルを備えている.テスト周波数は5MHz~50MHz.論理レベルは3.3Vまたは2.5V,デバイス電源は1V~3.8Vに対応している.

(a)DFTテスタ「Validator 500」

(b)デモンストレーションのようす

[写真2] DFTテスタ「Validator 500」のデモンストレーション

Validator 500の上にはコネクタが付いており,そこにターゲット・ボードを取り付ける.このターゲット・ボードは同社が提供するデザイン・ガイドに沿って作成する.Validator 500とパソコンをEthernetを介して接続し,デモンストレーションを行った.Validator 500の価格は780万円.

●最終テスト用メモリ・テスタが533MHzのDDR-II SDRAMに対応

アドバンテストは,DDR-II SDRAMに対応した最終テスト(パッケージング・テスト)用のメモリ・テスタ「T5593」を展示した(写真3).DDR-II SDRAMは,JEDEC(Joint Electron Device Engineering Council)によって標準化された次世代DRAMの規格である.データ転送速度400Mbps~667Mbps,電源電圧1.8Vなどを定義している.

本テスタのテスト周波数は,最大1.066GHzである.これにより,533MHz動作のDDR-II SDRAMのテストを行える.同時に測定できるメモリ・デバイス数は,最大128個である.

[写真3] 「T5593」の外観

今回のデモンストレーションでは,666MHz動作のSRAMを測定していた.

また,アジレント・テクノロジーは,波形解析機能を備えたフラッシュ・メモリの最終テストのデモンストレーションを行った(写真4).同社のウェハ・テスト用テスタ「V4100」に最終テスト用のインターフェース,およびDSI(Device Specific Interface)を介してメモリ・デバイスを取り付ける.DSIはデバイスごとに取り替える必要がある.最大32個のNAND型フラッシュ・メモリを同時に測定できる.

本製品を用いると,ピンごとに波形を表示できる.また,命令コードや期待値を設定できる.ブレーク・ポイントを設定する際にプログラミングは不要.OSはWindowsNTに対応している.ソフトウェアとして,Cコード・デバッガや波形生成ツールなどを提供する.出荷開始時期は,2003年2月の予定.

[写真4] V4100を用いたメモリ最終テスト

ウェハの良否を検査する「V4100」に,最終テスト用インターフェースとそれぞれのデバイス専用のインターフェースを接続し,検査するメモリ・パッケージをハンドラで搬送する.

●パターン・マッチング機能を搭載して,回転に対する検査能力を強化

コグネックスは,同社の外観検査装置「KV7100」に,パターン・マッチングの機能を追加した(写真5).従来,この機能を利用するには,別途提供される幾何学的パターン・マッチング・ソフトウェア「PatMax」を使ってユーザ自身がプログラミングを行い,同社の画像処理用ボード「MVS-8100D」などの設定を行う必要があった(写真6).

KV7100は,ICパッケージの検査やマーク検査,コネクタ検査などを行う.最大4台までのRS-170またはCCIRカメラを接続し,同時に四つの画像を取り込むことができる(ただし,高解像度カメラを使用する場合,日立国際電気の「KP-F100」を2台,RS-170またはCCIRカメラを1台接続可能).OSは,WindowsNT 4.0に対応している.入出力インターフェースとしては,2ポートのRS-232-C,1ポートのVGAを,32入力/32出力のパラレル・インターフェースを備えている.LV7100の1台目購入時の価格は299万円,2台目以降は199万円.

(a)KV7100の外観(写真右)

(b)検査画面

[写真5]KV7100のデモンストレーション

パターン・マッチング機能を追加したKV7100によるデモンストレーション.画像を取り込み,LSIパッケージ上の文字やピン数,ピンの間隔などを検査している.

[写真6]画像処理用ボード「8100D」と専用CMOSカメラ

CMOSカメラには,SXGA(解像度1,280×1,024)対応製品とVGA(同640×480)対応製品の2種類がある.

●研磨前からリソグラフィ,CMPプロセスまで,1台でウェハの形状を測定

KLA-Tencor Japanは,今回の展示会でウェハ形状測定装置「NanoPro NP1」の新製品を発表した.本計測装置は,ウェハ全体の形状や厚さ,平たん度のほか,ダイ単位の表面形状(ナノトポログラフィ)を測定する.解像度は0.3mm×0.3mm.ウェハの端から1mmのところまで計測できる.

本計測装置の特徴は大きく二つ.すなわち,1)ウェハを立てて計測する,2)光学干渉計技術を採用しており,斜入射を利用する.ウェハの3点を支え,立てて計測することで,横にウェハを置いた場合に起こる重力によるウェハ形状の歪みを防いでいる.また,裏面と表面を一度に測定できるという利点もある.一方,斜入射を利用すると,ウェハ面が荒いときでも干渉じまを観測できる.このため,研磨前の段階でウェハの良・不良を判断できるという.

本計測装置は,200mmウェハ用と300mmウェハ用の2種類を用意する.片面研磨加工ウェハ,両面研磨加工ウェハ,エピタキシャル・ウェハなどに対応する.

[写真7] KLA-Tencor Japanのブースのようす

関連記事: 一つ一つのチップにIDを付けて歩留まりを向上