[ keyword: EDA, IP, SoC ]

SynopsysとArteris,システム・レベル検証環境向けにオンチップ・バス・モデルを最適化して提供

ニュース 2012年2月16日

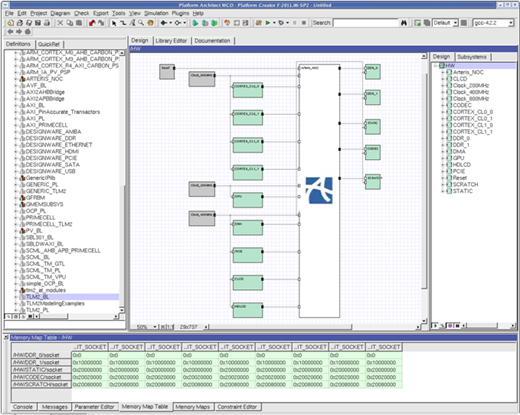

EDAベンダの米国Synopsys社とオンチップ・バスIP(インターコネクトIP)ベンダである米国Arteris社は,SoC(System on a Chip)などのシステム・レベル検証用シミュレーション・モデルの提供で協業することを発表した.Arteris社のオンチップ・バスIPである「FlexNoC」のTLM(Transaction Level Modeling)モデルを,Synopsys社のシステム・レベル検証ツール「Platform Architect MCO(Multicore Optimization Technology)」向けに最適化して提供する.専用のトランザクション生成機能や解析用のモニタ機能を用意した.SoC(System on a Chip)全体の性能評価やメモリ・サブシステムの性能評価,オンチップ・バスそのものの検証などに利用できる.

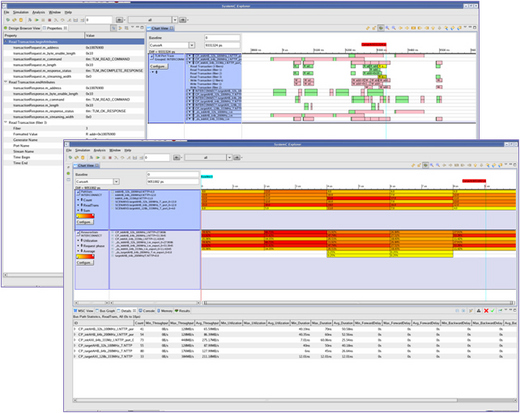

FlexNoCのTLMモデルの記述は,SystemC TLM-2.0規格に準拠しており,コーディング・スタイルはApproximately-timed(AT)に従っている.本モデルを利用することにより,シミュレーションの際のトランザクションの動きをトレースしたり,ポートの動作を解析することが容易になる.また,オンチップ・バス上の経路(パス)ごとに動作を解析することも可能.シミュレーションの実行中に,これらの解析に必要な情報を取り出せる仕組みをTLMモデルに組み込んだ.

FlexNoCは,Neowork on Chip(NoC)と呼ばれる技術を利用したオンチップ・バスのIPコアである.CPUコアやメモリ・ブロック,周辺回路ブロックの間の通信を,パケット方式のネットワーク接続によって実現する.複雑な構造のオンチップ・ネットワークを最適設計することで,回路規模や消費電力を改善できるという.

[図1] Platform Architect MCOの画面例(オンチップ・バスにトランザクタやメモリ・モデルを接続したところ)

[図2] Platform Architect MCOの画面例(トランザクションの動きをトレースした解析画面)

■価格 |

■連絡先 |