[ keyword: LSI ]

Lattice,SERDES搭載の低コストFPGAファミリと無償の32ビット・ソフトCPUコアを発売

ニュース 2006年9月19日

米国Lattice Semiconductor社は,最大3.125GbpsのSERDESを搭載する低価格のFPGAファミリ「LatticeECP2M」を発売した.また,無償で利用できるソフト・マクロの32ビットRISC CPUコア「LatticeMico32」の提供を開始した.

LatticeECP2Mは,約6,000~68,000個の4入力LUT(ルックアップ・テーブル),66~288個の18Kビット・メモリ・ブロック,最大で3.125Gbpsに対応する4~16個のSERDESブロック,8個のアナログPLL(phase-locked loop),2個のディジタルPLL(DLL)などを持つ.高速シリアル・トランシーバは,PCI ExpressやギガビットEthernet,Serial RapidIOなどの規格に対応する.また,これらのプロトコル処理のための回路も内蔵する.プログラム素子はSRAMセルである.電源電圧はコア電圧が1.2V.「LatticeECP2M-35」の出荷は2006年10月から,それ以外の品種の出荷は2007年上半期から開始する.

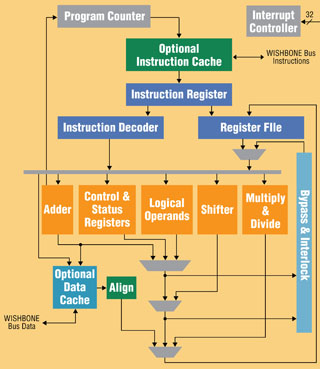

LatticeMico32は,HDLソース・コードの形で提供する.ライセンスおよびロイヤリティは無償である.性能と規模のトレードオフに基づいたカスタマイズが行える.LatticeECP2への実装時の最高性能構成では,回路規模が2300LUT,動作周波数が110MHz(暫定値)である.周辺回路として,非同期SRAMコントローラやオンチップ・メモリ・コントローラ,32ビット・タイマ,DMAコントローラ,汎用I/O,I2Cマスタ・コントローラ,SPI,UARTを提供する.これらは,オープン・ソースのWishboneバス・インターフェースに対応する.ソフトウェア開発環境は,GNUベースのコンパイラ,アセンブラ,リンカ,デバッガを提供する.

[図1] LatticeMico32のブロック図

[写真1] LatticeECP2Mファミリの外観

[表1] LatticeECP2Mファミリの概要

型名

ECP2M-20

ECP2M-35

ECP2M-50

ECP2M-70

ECP2M100

ルックアップ・

テーブル数19K

34K

48K

67K

95K

18Kビット・メモリ・

ブロック数66

114

225

246

288

18×18ビット

乗算器数24

32

88

96

168

PLL/DLL数

8/2

8/2

8/2

8/2

8/2

最大ユーザI/O数

301

411

457

449

601

最大SERDES数

4

4

8

16

16

パッケージ

256ピンFBGA

484ピンFBGA484ピンFBGA

672ピンFBGA484ピンFBGA

672ピンFBGA

900ピンFBGA900ピンFBGA

900ピンFBGA

1156ピンFBGA

■価格 |

■連絡先 |