信号線当たり100Gビット/秒の超高速伝送を実現する技術とは? ―― テクトロニクス/ケースレー イノベーション・フォーラム2013

●回路技術で伝送路の損失を補償

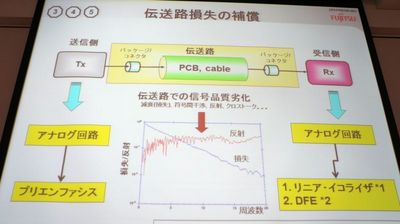

プリント基板,コネクタ,ケーブルなどの部品を高周波対応品に換えることは,コストの増大を招く.また高周波対応品でも高周波損失はゼロではないので,根本的な対策になるとは限らない.そこで,送信回路と受信回路に伝送損失を補償する回路を付加し,総合的なコストの増大を抑えることが最近の高速信号伝送では増えてきた(写真6).

写真6 伝送路の損失を補償する回路技術

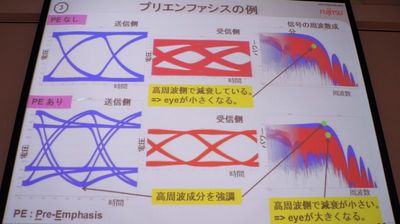

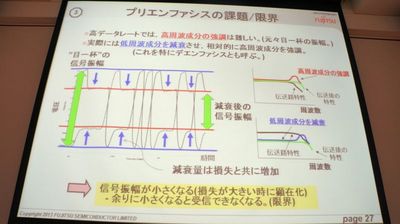

送信側での代表的な補償回路が「プリエンファシス(pre-emphasis)」である.プリエンファシスでは,伝送路損失の周波数特性を補償するように送信信号の周波数特性を調整する.例えば高周波での損失が大きい伝送路では,プリエンファシスによって信号の高周波成分を強調する(写真7).ただし実際には伝送速度が高いと,高周波成分を強調することは難しい.そこで逆に低周波成分を減衰させ,相対的に高周波成分を強調する(写真8).

写真7 プリエンファシスの例

写真8 プリエンファシスの課題と限界

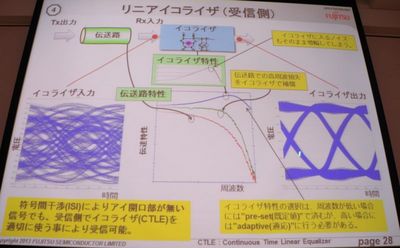

受信側での代表的な補償回路が,「リニア・イコライザ(CTLE:Continuous Time Linear Equalizer)」と「DFE(Decision Feedback Equalizer)」である.前者は「連続時間線形等化器」,後者は「判定帰還型等化器」とも呼ぶ.リニア・イコライザは伝送路の周波数特性を補償するような周波数特性を備えた増幅回路である.適切な特性を与えれば,信号波形をきれいに整形することも可能だ(写真9).

写真9 リニア・イコライザの例

波形の歪みがそれほど大きくないときは,リニア・イコライザが有効である.しかし波形の歪みが大きくなると,リニア・イコライザでは補償が難しくなる.このような波形歪みを補償するのがDFEである.DFEは,受信信号の論理値を決定する判定器(サンプラー)と,サンプリングした信号に遅延と重み付け(タップ係数)を与える回路(タップ)で構成される.タップの数を増やすと,受信信号をきめ細かく補償できるようになる.

●アナログ補償からディジタル補償へ

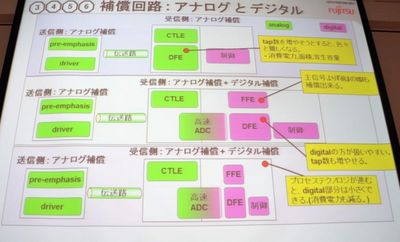

補償回路は,伝送速度がそれほど高くないときはアナログ回路で実現できた.しかし伝送速度が高くなると,受信側で補償する回路の規模が大きくなる.特に問題なのは,DFEのタップ数を増やすことによる回路規模とシリコン面積,消費電力の増大である.そこで補償回路をディジタル化するという考えが出てきた(写真10).

写真10 アナログ補償回路とディジタル補償回路

アナログ補償回路はリニア・イコライザだけとし,この後段に高速のアナログ・ディジタル変換回路を付加する.ディジタル化した信号をディジタル回路のDFEで補償する.ディジタル補償回路はシリコン製造技術の微細化によってシリコン面積を小さくし,消費電力を低減できるので,アナログ補償よりも有利になる.