日本の超多層プリント基板がギネス世界記録に認定 ―― JPCA Show 2013

●部品内蔵基板の製造サービスを提供

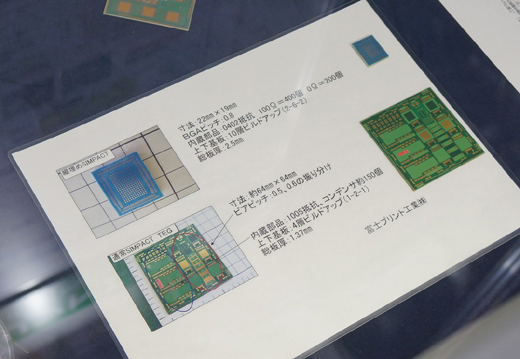

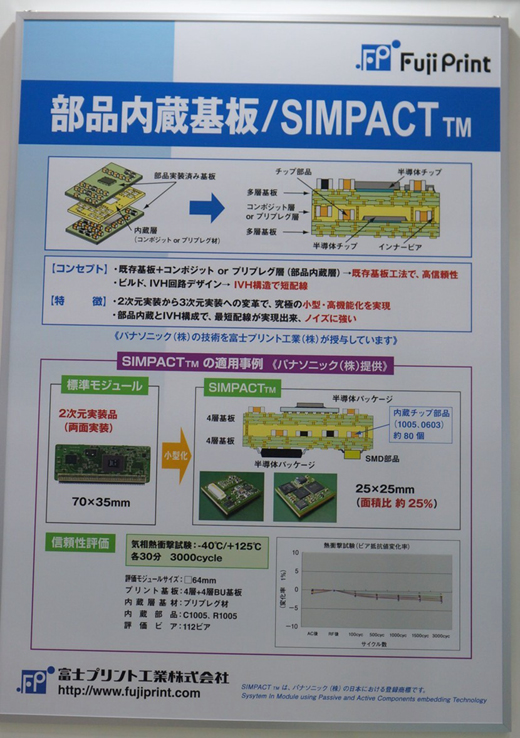

また富士プリント工業は,パナソニックが開発した部品内蔵基板技術「SIMPACT」をライセンス導入し,部品内蔵基板の製造サービスを提供していることをアピールしていた(写真9).多層基板の内層をプリプレグあるいはコンポジットとし,半導体チップやチップ部品などを埋め込む.ブースでは,実際に試作した部品内蔵基板を展示していた(写真10).

写真9 多層基板の内層をプリプレグあるいはコンポジットとし,半導体チップやチップ部品などを埋め込む部品内蔵基板の説明パネル

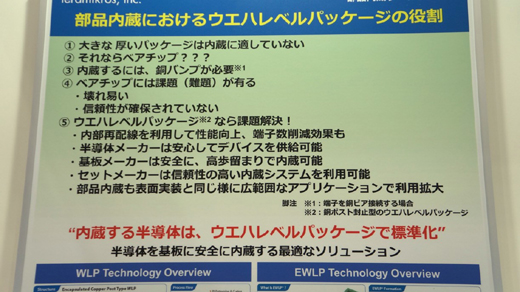

●シリコン・ダイとほぼ同じ大きさのパッケージで基板に内蔵

部品内蔵基板に半導体チップを内蔵させる場合,通常のパッケージではかさばり,埋め込みが簡単ではない.かといってシリコン・ダイのベア・チップでは信頼性に問題がある.そこでテラミクロスは,シリコン・ダイとほぼ同じ大きさのパッケージである「ウエハーレベルパッケージ」を解決策として提案していた(写真11).

写真11 部品内蔵基板における「ウエハーレベルパッケージ」の役割を説明したパネル

採用例として,カシオ計算機の腕時計用基板を展示していた(写真12).文字盤のバックライト用ドライバICとEEPROMを埋め込んでいる.ドライバICの大きさは1.44mm×1.05mm.厚みは0.63mm.EEPROMの大きさは1.53mm×1.28mm.厚みは0.63mmである.

写真12 「ウエハーレベルパッケージ」を埋め込んだ基板の採用事例

カシオ計算機の腕時計用基板.

さらに,シリコン・ダイから「ウエハーレベルパッケージ」を作成する工程を,模型で分かりやすく展示していた(写真13,写真14).通常のパッシベーション膜の上に保護膜を形成し,シリコン・ダイの電極パッドから銅配線を引き出して電極パッドを再配列する.再配列した電極パッド(銅)にはんだボールを載せると,パッケージが完成する.またプリント基板に埋め込むときは,はんだボールを載せず,銅の電極パッドとプリント基板の内層配線を接続する.

写真13 「ウエハーレベルパッケージ」の製造工程(前半)

左はシリコン・ダイに保護膜(絶縁膜)を再形成したところ.右は左の続きで,再配線レイアウト形成と銅ポスト形成,アンダーバンプ・メタル・エッチング(UBMエッチング)を施したところ.

写真14 「ウエハーレベルパッケージ」の製造工程(後半)

左は樹脂封止と電極露出,裏面研削を実施した後の状態.右は左の続きで,はんだボールを取り付けたところ.

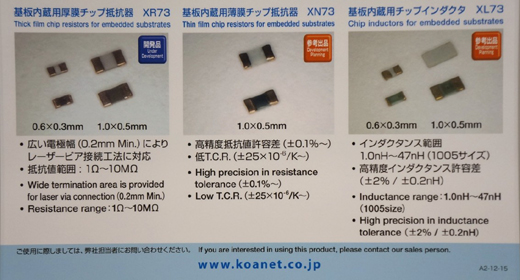

●プリント基板の層間埋め込み用チップ部品を展示

KOAは,多層プリント基板の配線層間に内蔵することを想定したチップ部品を参考展示していた(写真15).チップ抵抗器とチップ・インダクタがある.層間に埋め込むために厚みを0.15mmと極めて薄くしたほか,電極材料を銅に変更する,電極の幅を広げる,といった工夫を施した(写真16).

写真15 多層プリント基板の配線層間に埋め込むために開発したチップ部品(開発品と参考展示)の説明パネル

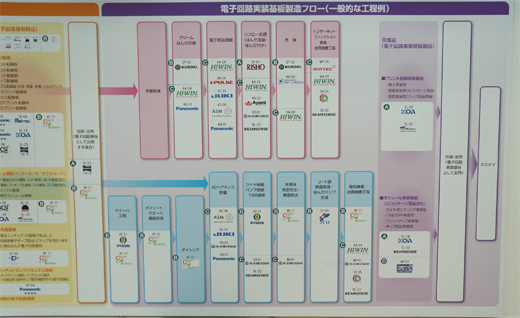

●電子回路基板のサプライ・チェーンをパネル展示

このほか,会場内には電子回路基板のサプライ・チェーンを図示した巨大なパネルが置かれており,来場者が足を止めていた.電子回路基板の設計から製造までのフロー・チャート(写真17)と,プリント基板の製造に関わるサプライ・チェーンの説明図(写真18),プリント基板に部品を実装する工程にかかわるサプライ・チェーンの説明図(写真19)である.サプライ・チェーンにかかわる企業のロゴ・マークと出展場所が掲示されており,力の入れようがうかがえた.

写真18 プリント基板の製造フローとサプライ・チェーンの説明図

写真19 プリント基板に部品を実装するフローとサプライ・チェーンの説明図

ふくだ・あきら

フリーランステクノロジーライター

http://d.hatena.ne.jp/affiliate_with/