次世代64ビット対応ISA「ARMv8」や最新コア「Cortex-A7」に注目 ―― ARM TechCon 2011

CPUコア・ベンダである英国ARM社は,2011年10月25日~27日に米国カリフォルニア州Santa Claraで電子機器やLSIの開発技術者向けのイベント「ARM TechCon 2011」を開催した(写真1).本イベントでは,64ビット実行モードを用意した新しい命令セット・アーキテクチャ「ARMv8」や,最新コアである「Cortex-A7」などの情報が公表され,来場者の注目を集めていた.

写真1 ARM TechCon 2011の会場となったSanta Clara Convention Center

●64ビット・コンピューティングを初めて導入へ

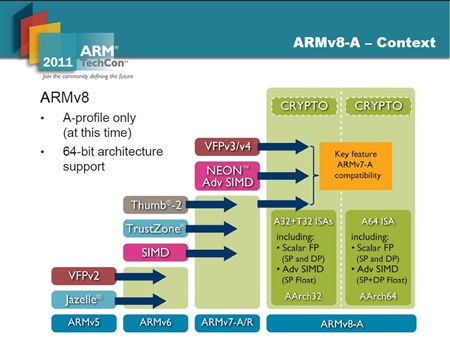

このイベントでARM社は,次世代CPUの命令セット・アーキテクチャ(ISA:Instruction Set Architecture)「ARMv8」を発表した.ARM社はこれまで,32ビットRISC型CPUのISAを開発してきた.最新世代のISAは「ARMv7」である.「ARMv8」ではARM社のCPUとしては初めて,64ビット・コンピューティングを導入する.

ARMv8では,64ビット実行モードの「AArch64」と32ビット実行モードの「AArch32」が用意されており,両者を切り換えて処理を実行する(図1).64ビット実行モードの「AArch64」は,まったく新しい命令セット「A64」を有する.32ビット実行モードの「AArch32」は,ARMv7アーキテクチャとの互換性を保つ.

図1 ARMコアの次期命令セット・アーキテクチャ「ARMv8」の位置付け

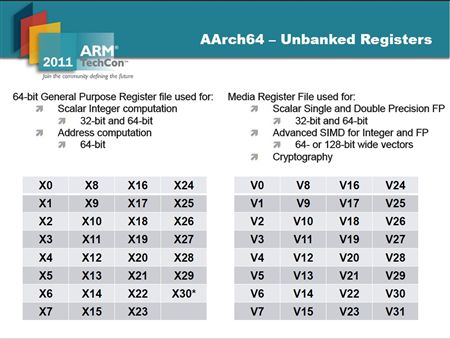

64ビット実行モードの「AArch64」は,命令セット「A64」のほか,例外処理機構,セキュリティ機構,仮想化支援機構,メモリ空間の変換機構などで構成される.命令長は32ビットの固定長である.物理アドレス空間は最大48ビットであり,256T(テラ)バイトのメモリ空間を有する.搭載するレジスタは64ビットの汎用レジスタが31本と128ビットのメディア・レジスタが32本(図2).浮動小数点演算では倍精度演算に対応した.ページ・サイズには,4Kバイトと64Kバイトの2種類がある.

図2 ARMv8のレジスタ・ファイル

ARMv8の詳しい内容は2012年後半に公表される予定.ARMv8を実装したCPUコアも,2012年中に登場する計画となっている.

●ハイエンドのスマートフォンを2年後にローエンド化

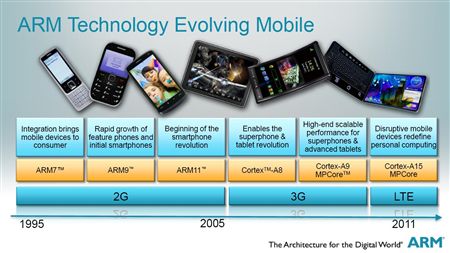

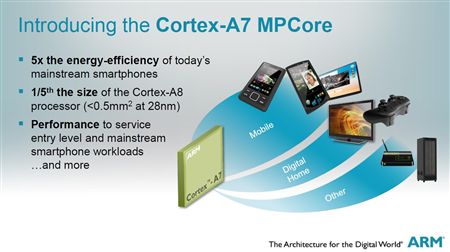

「ARMv7」を実装したCPUコアとして,次期アプリケーションCPUコア「Cortex-A7」の内容をARM社が公表した.2年後の2013年には,このCPUコアを搭載したSoC(System on a Chip)とスマートフォンが市場に登場し始めるとみられる(図3).

図3 アプリケーションCPUコアの変遷と携帯電話端末の進化

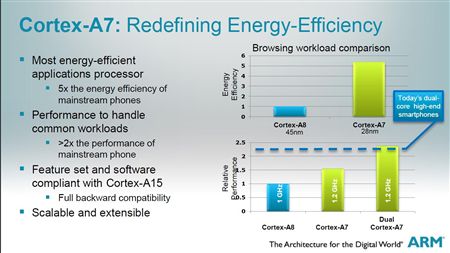

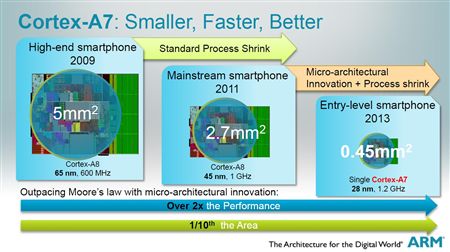

「Cortex-A7」は,2011年現在,500ドルほどするハイエンド機種のスマートフォンと同等の性能を,2013年に100ドル以下のエントリ・モデルのスマートフォンで実現することを狙って開発した.28nmプロセスで製造したときのシリコン面積は0.45mm2(平方ミリ)ときわめて小さい(図4).すなわち製造コストが低い.またARM社のアプリケーションCPUコアとしては,エネルギー効率が最も高い.

図4 Cortex-A7コアの概要

Cortex-A7コアの動作周波数は,28nmプロセスで製造したときに最大1.2GHzと非常に高い.最新に近いハイエンドのアプリケーションCPUコア「Cortex-A8」を40nmプロセス(現在の最先端量産プロセス)で製造したときの動作周波数が最大1GHzなので,現在のハイエンドコアよりも高い周波数で動くことになる(図5).

図5 Cortex-A8コアとCortex-A7コアのシリコン面積比較

消費電力については,28nmプロセスで製造したCortex-A7コアのエネルギー効率は,45nmプロセスで製造したCortex-A8コアの約5倍に達する(図6).また演算処理の性能も,Cortex-A7はCortex-A8よりも高いとしていた.

図6 Cortex-A7コアのエネルギー効率と演算処理性能