MicrosoftのKinectの技術概要やIBMの次期スパコン用プロセッサなどが登場 ―― Hot Chips 23

●パソコン向けにCPUとGPUを統合

パソコン用プロセッサでは,グラフィックス処理ユニット(GPU)を内蔵した大規模プロセッサの技術内容を米国Intel社と米国AMD(Advanced Micro Devices)社がそれぞれ発表した.いずれもCPUのほかにGPUと2次キャッシュ,DDR3メモリ・コントローラ,PCI Expressインターフェースなどを1チップのシリコン・ダイ上に集積している.

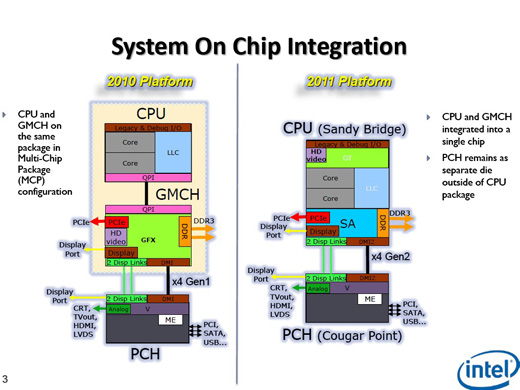

Intel社は第2世代のCoreプロセッサ(開発コード名「Sandy Bridge」)の概要を説明した(図8,図9).4個のCPUコアと4ブロックの2次キャッシュ,システム・エージェント(メモリ・コントローラや入出力インタフェースをまとめた回路),GPUで構成されている.

図8 前世代のプラットフォームと「Sandy Bridge」世代のプラットフォームの違い

前世代ではCPUとGPUが別のシリコン・ダイになっており,両方のダイを一つのパッケージに収納することで一つのLSIに見せていた.Sandy Bridgeでは,それが完全に1チップのシリコン・ダイにまとめられた.

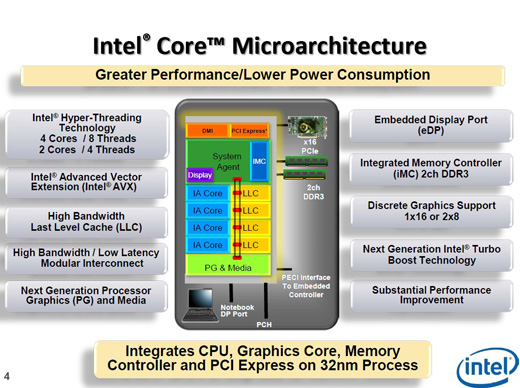

図9 「Sandy Bridge」の内部ブロックと要素技術

製造技術は32nmである.

特徴は,CPUコアと2次キャッシュ,GPU,システム・エージェントの間をリング状のバスで結んだことである(図10).リング状バスのノード間が最短距離で結ばれるので,データの転送による遅延時間がきわめて短くなるという.

図10 リング状バスの概要

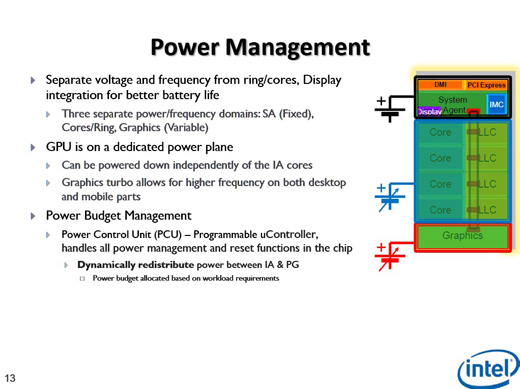

電源ドメインは三つに分かれている.システム・エージェント,CPUコアおよび2次キャッシュ,GPUである.消費電力を低減するため,それぞれの電源ドメインは独立に電源をシャットダウンできる(図11).

図11 電源ドメインの概要

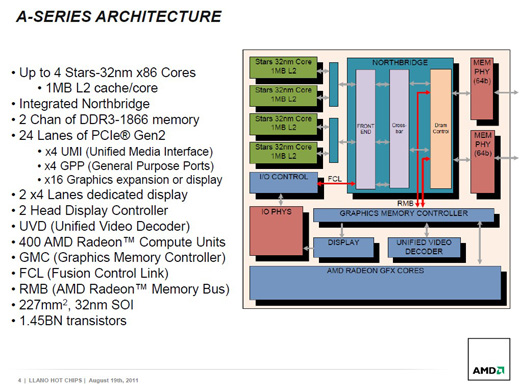

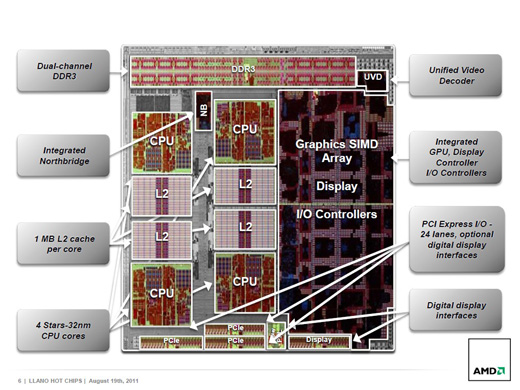

AMD社は「AMD A-シリーズ」プロセッサ(開発コード名「Llano」)の概要を説明した(図12,図13).4個の2次キャッシュ内蔵CPUコア,GPU,DDR3メモリ・コントローラ,ビデオ・デコーダなどで構成されている.製造技術は32nmのSOI CMOS技術,トランジスタ数は14億5,000万トランジスタ,シリコン・ダイ面積は227平方ミリ.

図12 「AMD A-シリーズ」プロセッサの概要と内部ブロック図

図13 「AMD A-シリーズ」プロセッサのシリコン・ダイの写真とレイアウト図

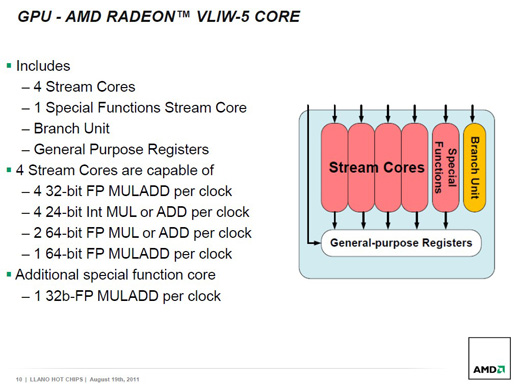

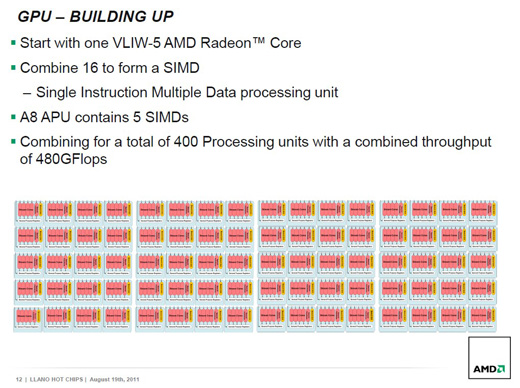

特徴は,強力なGPUを搭載していることである.VLIW(Very Long Instruction Word)方式のコアを数多くならべることで,高いグラフィックス演算性能を実現した.1個のコア・ユニットは,4個のストリーム・コアと1個の特殊ストリーム・コア,分岐ユニット,汎用レジスタで構成されている(図14).このコア・ユニットを16個使って,1個のSIMD(Single Instruction Multiple Data)プロセッサ・コアを構成する.そして最大5個のSIMDプロセッサ・コアでGPUを実現している(図15).このときのピーク演算性能は,480GFLOPSに達する.

図14 GPUを構成するVLIWコアの概要

図15 GPUの構造.最大で80個のVLIWコアを使う

ふくだ・あきら

フリーランステクノロジーライター

http://d.hatena.ne.jp/affiliate_with/