SSDが高速性を誇示,NAND型フラッシュは低コストの64Gビット品が登場 ―― Flash Memory Summit 2010

●3ビット/セル技術の64GビットNANDフラッシュ・メモリ

NAND型フラッシュROMの分野では,米国Intel社と米国Micron Technology社が8月17日に,3ビット/セル技術(TLC技術)による64Gビットの大容量NAND型フラッシュROMを共同開発し,出荷を始めたと発表した.シリコン・ダイ面積が131mm2と64GビットのNAND型フラッシュROMとしては最も小さく,理論的には製造コストが低い(写真7).製造技術は25nmのCMOSプロセスである.なおIntel社とMicron Technology社の両社が2ビット/セル技術(MLC技術)と25nmプロセスで開発済みの64GビットNAND型フラッシュROMは,シリコン・ダイ面積が167mm2.MLC技術からTLC技術に変更することで,シリコン・ダイ面積は約78%に減少している.

写真7 3ビット/セル技術による64GビットNAND型フラッシュROMのシリコン・ダイ

本展示会のMicron Technology社のブースには,3ビット/セル技術(TLC技術)による64GビットNAND型フラッシュROMを作り込んだシリコン・ウェハの実物が,展示されていた(写真8).直径300mmのウェハである.

写真8 3ビット/セル技術による64GビットNAND型フラッシュROMを作り込んだシリコン・ウェハ

●エンタープライズSSDの共通規格に準拠したコントローラ

エンタープライズ向けサーバとNAND型フラッシュROM用コントローラの共通インターフェース規格に,Enterprise NVMHCI(Non-Volatile Memory Host Controller Interface)がある.Intel社が中心となって策定している,ホストとフラッシュROMコントローラを結ぶ共通仕様で,PCI Express対応SSDとホスト・マシンの間のプログラミング・インターフェースを規定する.2010年第4四半期には仕様が固まる予定だ.そのEnterprise NVMHCIに準拠したコントローラを,米国IDT(Integrated Device Technology)社が展示していた.

コントローラはシリコン・チップではなく,FPGAを並べた開発ボードにコントローラ回路を格納したもの(写真9).NAND型フラッシュROMおよびサーバと接続して実際に動かしてみせていた.サーバとコントローラの接続にはPCI Express Gen 1を4レーン使っている.

写真9 Enterprise NVMHCI準拠のコントローラを格納した開発ボード

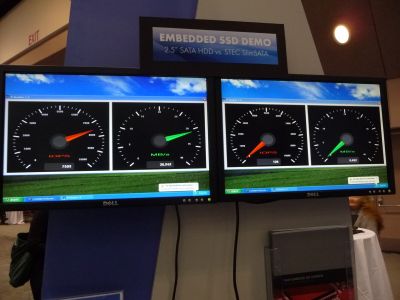

●SSDの高速性と低消費電力性を動作展示でアピール

このほかSSDベンダの米国STEC社は展示ブースで,SSDとHDDの入出力速度,データ転送速度,消費電流を比較するデモンストレーションを実施していた(写真10,写真11).SSDは同社の32Gバイト品,HDDは米国Western Digital社の160Gバイト品(回転速度は5400rpm)である.

入出力速度(IOPS)はSSDが7503,HDDが120,データ転送速度はSSDが約31Mバイト/s,HDDが約0.5Mバイト/sといずれもSSDが優っていた(写真10).また,消費電流はSSDがHDDの5分の1くらいだった.

写真10 入出力速度(IOPS)とデータ転送速度をSSD(左)とHDD(右)で比較してみせた

写真11 SSD(左)とHDD(右)のセットアップ

隣に置いたメータは電流計である.

ふくだ・あきら

フリーランステクノロジーライター

http://d.hatena.ne.jp/affiliate_with/

Post a Comment