動作合成とC/C++/SystemC/SystemVerilogの協調設計 ―― Cynthesizerの活用事例

6. 適用事例

筆者らは本稿で説明したフローに従って,顔認識エンジンFSE(Face Sensing Engine)の顔検出・追跡アルゴリズムに対してIPコア化を実施しました(3).

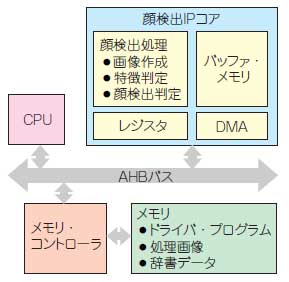

図7にIPコアの構成を示します.IPコアとしてアルゴリズムに対応する演算部のほかに,制御レジスタ,DMAコントローラ,バッファ・メモリから構成されています.図中の顔検出処理部が,顔検出・追跡アルゴリズムの演算部分を動作合成してハードウェア化した部分です.インターフェースとしてAHBバスを採用し,CPUとはAHBバスを経由してアクセスします.DMAコントローラはメモリからバッファ・メモリへの転送に用います.

図7 画像処理IPコアのブロック図

写真1に顔検出を実施した例を示します.顔検出のIPコアでは,画像データを解析し,解析したデータと顔判定辞書とのマッチングで,顔と判定した一つまたは複数のく矩形領域の座標を出力します.写真1は顔と判定された領域の矩形図を入力データに対して重ね合わせたものです.今回はARM926とFPGAを搭載したボードを使用しました.FPGAにはハードウェア化したモデルを実装し,ハードウェア化の対象にならなかったアルゴリズムのフロントエンド部分はソフトウェアとしてARM926上で動作させました.

写真1 FSE実行結果の例

ARM926とFPGAを搭載したボードを利用した.

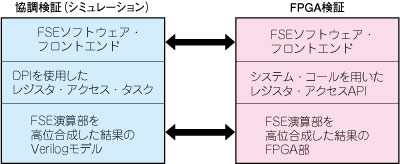

図8に協調検証の階層からFPGA検証での階層への変換を示します.協調検証では,前章で説明したようにDPIを介してソフトウェアからハードウェア・モデルにアクセスを実施します.FPGA検証ではDPIの代わりにシステム・コールを用いて,ソフトウェアからFPGA上のハードウェア・モデルへアクセスするようにします.

図8 協調検証とFPGA検証との階層関係

このように介在する層を変えるだけで協調検証からFPGA検証へ持っていくことができますので,上位のソフトウェアや下位のハードウェアの変更をする必要がなくなります.このため協調検証シミュレーション環境からFPGA環境への展開や,FPGA検証から協調検証へのフィードバックなどが容易かつ,短期間にできるようになりました.

このようなハードウェア化を行うことで,ソフトウェア単体だけの場合に比べ,動作周波数を低下させてもリアルタイムに顔を検出できました.

参考・引用*文献

(1 ) 桜井至;SystemCによるビヘイビア合成入門,Design Wave Magazine,2004年11月号~2005年9月号.

(2 ) 宮下晴信;続・SystemVerilogで簡易CPUバス・モデルを記述,Design Wave Magazine,2004年12月号.

(3 ) 顔認識エンジンFSE紹介サイト,沖電気工業.

http://www.oki.com/jp/fse/

しぶや・たかとし

うつみ・いさお

もり・よしかず

(株)沖ネットワークエルエスアイ

<筆者プロフィール>

渋谷貴利.1992年沖電気工業入社.2002年沖ネットワークエルエスアイ設立と同時に移籍.入社以来,LSI設計,SOC設計に携わる.日ごろ思うことは「何事も勉強しておいて損は無い」.心掛けていることは「Simple is best」.

内海功朗.1986年沖電気工業入社.2002年沖ネットワークエルエスアイ設立と同時に移籍.入社以来,LSI設計,SOC設計に携わる.顔識別機能でなにか低価格のおもちゃができないか思案中.最近,環境存在論に興味を持っている.

森 義一.1981年沖電気工業入社.2002年沖ネットワークエルエスアイ設立と同時に移籍.入社以来,プロセッサ開発,SOC設計に携わる.顔画像処理技術の登場で,SF映画の世界であるロボコップやターミネーターの実現に向けて1歩を踏むと思うとワクワクしている.