動作合成とC/C++/SystemC/SystemVerilogの協調設計 ―― Cynthesizerの活用事例

2.ハードウェア化の方針と設計の流れ

今回,筆者らが採用したハードウェア化の方針は以下のようなものです.

- ハードウェアとソフトウェアの協調設計とする.

- ソフトウェアの関数単位でハードウェアを実現する.

- ソフトウェア機能を一切変更しない.

以下,その理由を説明します.

● 必ず実行され負荷の大きな部分をハードウェア化する

複雑かつ規模の大きなソフトウェアをすべてハードウェア化すると,多大な労力を必要とします.一方,ソフトウェアの中身を見ると例外的な処理への対応などが,かなりの部分を占めています.そこで,ソフトウェアの中で必ず実行され,かつ負荷の大きな部分に着目してハードウェア化を行うことで,開発の規模を限定でき,結果として開発が容易になります.

関数単位のハードウェア化については,ソフトウェアと同じ構成とすることで分割単位やパラメータの類がハードウェアとソフトウェアで共通化できます.この結果,性能よりもハードウェア規模の小ささを追求する場合は,ハードウェア化した関数を使わずにソフトウェアに戻せば要求に応えることができます.ハードウェアもモジュール化して開発しておくことで,さまざまな要求に応えることが可能になります.

● ソフトウェアの機能は下げない

従来の人手によるハードウェア設計では,開発を進めるために処理方式そのものを簡略化する,ハードウェア量を削減するためにビット精度を犠牲にする,というようなことが行われていました.動作合成を使用することで,基本的にはそのままソフトウェア機能をハードウェア化できます.また,ハードウェア規模の問題はもはや大きな問題ではなくなってきています.優れたソフトウェアの機能を変えることはソフトウェアの価値をも下げてしまうものと考えられます.筆者らはソフトウェアに最大の価値を置き,処理に関する変更は行いませんでした.

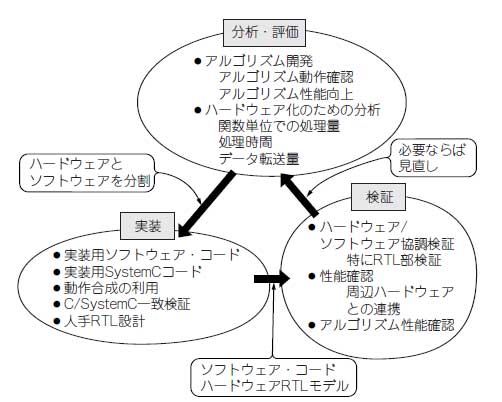

● 設計の流れは分析,実装,検証

ソフトウェアのハードウェア化を行う場合に,どのような手順を踏むでしょうか.図1に設計の流れを示します.筆者らは工程を大きく三つに分けました.分析,実装,検証です.この工程はRTLコードをシミュレーション段階で確認するところまでとしています.実際にはこの後,RTLコードから合成された回路をFPGAで動作させ,実機に近い環境で各種の評価を行います.

図1 ソフトウェアのハードウェア化の流れ

実際にはこの後RTLをFPGAに書込み,実機に近い環境でさまざまな評価を行う.

最初にハードウェア化を行う対象を決定するための分析を行います.ここではソフトウェアを実行した結果からプロファイリングを採取し,ハードウェア化する部分を決定します.

次にハードウェア化する関数を決定後,それを動作合成してRTLコードを生成します.最初に対象となるプログラムを動作合成可能なSystemCコードなどに書き換え,オリジナルのプログラムとの一致性を確認します.そして一致を確認後,動作合成を実行して性能・面積をできるだけ意図したところに近づけたRTLコードを生成させます.動作合成ツールを適用しないハードウェア部については人手でRTL設計を進めます.これが実装段階です.

そして,動作合成および人手設計したRTLコードとソフトウェアを組み合わせた協調検証を実施する検証段階へ移行します.ここでは各ハードウェアのインターフェースや論理のデバッグに加え,ソフトウェアとのインターフェースをシミュレーションによって確認します.この段階を踏むことで,FPGAでの評価などといった後工程作業を円滑に進められます.それでは次項から各工程の詳細について説明します.