EMCやノイズ対策でコンデンサやバリスタの高性能化と小型化が進展 ―― EMC JAPAN 2009レポート

電磁環境整合技術とノイズ対策技術に関する展示会「第22回EMC・ノイズ対策技術展(EMC JAPAN 2009)」が2009年4月15日~17日に幕張メッセ(千葉県千葉市)で開催された(写真1).出展社数は93社,出展小間数は238小間だった.

[写真1] EMC JAPAN 2009展示会場の様子

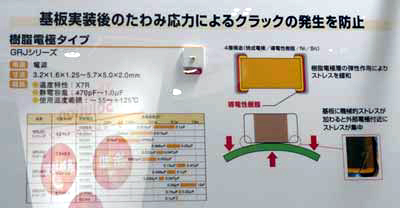

●クラック対策を施した積層セラミック・コンデンサ

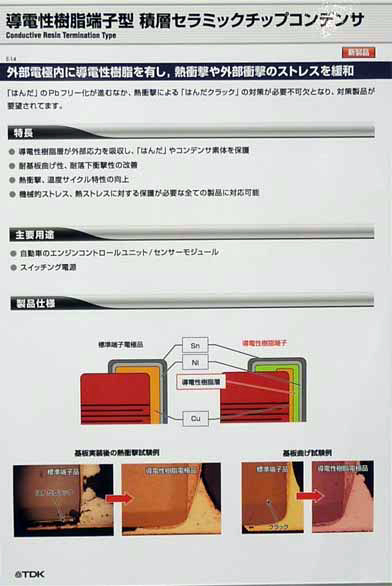

電源回路のバイパスやデカップリングなどに使われる積層セラミック・コンデンサでは,機械的なひずみによるクラック(ひび割れ)への対策を施したチップ型積層セラミック・コンデンサを村田製作所とTDKがそれぞれ展示した.

チップ型積層セラミック・コンデンサをはんだ付けしたプリント基板がたわむと,コンデンサに応力が加わってクラックが入ることがある.クラック対策品では,電極に導電性樹脂層を設けて応力を緩和させた.

村田製作所は「GRJシリーズ」の名称で製品化し,大きさが3.2mm×1.6mm~5.7mm×5.0mm,静電容量が470pF~0.1μFの品種を用意すると展示パネルで説明していた(写真2).

[写真2] 村田製作所のGRJシリーズ

電極が4層構造になる.セラミック側から焼成電極,導電性樹脂,ニッケル,スズである.

TDKは熱衝撃試験と基板曲げ試験を実施した結果を,パネルで紹介していた(写真3).対策品によって,前者の試験でははんだクラックがなくなり,後者の試験ではコンデンサ本体のクラックがなくなる.

[写真3] TDKの導電性樹脂端子型 積層セラミック・チップ・コンデンサ

こちらも電極は4層構造.セラミック側から銅,導電性樹脂,ニッケル,スズとなる.

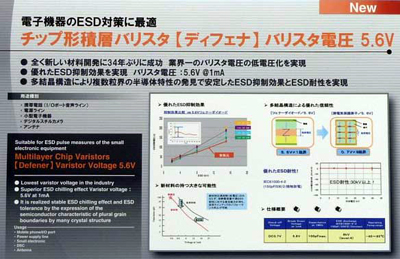

●バリスタの低電圧化と小型化が進む

静電気放電(ESD:Electrostatic Discharge)や雷放電などによる電圧サージを抑制するチップ型積層バリスタでは,パナソニックが低電圧品を,TDKが超小型品を展示していた.

パナソニックは,バリスタ電圧が5.6V(電流1mA)と低いチップ型積層バリスタ「ディフェナシリーズ」を展示した(写真4).同社の既存製品では,6.8Vがバリスタ電圧の最小値だった.バリスタ素子の材料を新たに開発することで,バリスタ電圧を低減したという.大きさが1.0mm×0.5mm(1005サイズ)のバリスタをまず製品化する.2009年6月にサンプル出荷を始め,同年9月に量産を始める予定である.サンプル価格は1個5円から.

TDKは,外形寸法が0.4mm×0.2mmと小さなチップ型積層バリスタ「AVR0402」シリーズを展示した.バリスタ電圧は12V(電流1mA)である.

[写真4] バリスタ電圧が5.6Vと低いチップ型積層バリスタ「ディフィナ」の説明パネル

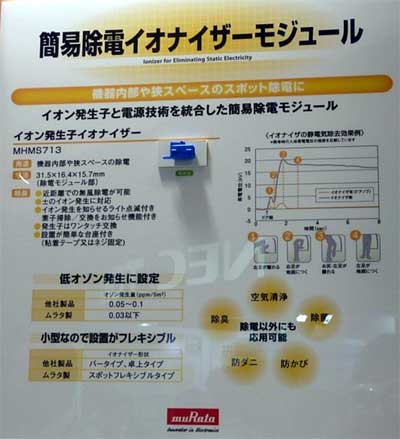

●イオンで局所的に静電気を取り除く

工場の生産ラインやクリーン・ルームなどで製造装置や治具などの帯電を防ぐ装置にイオン発生装置(アイオナイザあるいはイオナイザ)がある.村田製作所は,局所的にイオンを吹き付けて静電気を取り除く小さなモジュールを開発し,参考品を展示していた.「簡易除電イオナイザーモジュール」と呼んでいる(写真5).展示ブースでは絶縁体の板を帯電させるとともに,「簡易除電イオナイザーモジュール」で除電し,表面電位計で帯電電位を測定して除電効果を示していた(写真6).

[写真5] 村田製作所の「簡易除電イオナイザーモジュール」の説明パネル

[写真6] 「簡易除電イオナイザーモジュール」のデモンストレーション

右側の手の甲を模った物体を帯電させ,モジュールで除電してみせていた.