Cadence,国内2社の導入事例とともに満を持してビヘイビア合成ツールを発表 ―― 機能が共通で要求性能の異なる再利用IP設計で本領を発揮

米国Cadence Design Systems社は,ビヘイビア合成ツール「C-to-Silicon Compiler」を発表した.2008年7月17日~18日に開催された同社の日本におけるプライベート・ショウ「DA SHOW/CDNLive! Japan 2008」にて,日立製作所,およびルネサス テクノロジによる導入事例の発表が行われた.EDAツールの新製品発表と同時に,ユーザによる導入事例が発表されるケースは珍しい.両社は約2年前から本ツールの評価・開発などでCadence社に協力しているという.Cadence社は,本ツールを使用することによって,IP(Intellectual Property)コア開発の生産性を従来の10倍に引き上げられると述べている(写真1).

[写真1] DA SHOW/CDNLive! Japan 2008のために来日したC-to-Silicon Compilerの担当者

左からCadence社 Director, Field Operations, C2SiliconのMark Warren氏,同社Group Director, Marketing, System Design and VerificationのRan Avinun氏,同社Vice President & General Manager, C-to-SiliconのMichael McNamara氏.

●入力記述はSystemC,出力記述はVerilog HDL

ビヘイビア合成ツールとは,クロックや使用する演算器などの詳細が確定していない抽象度の高い設計記述(アルゴリズム記述)から,これらが確定したRTL(Register Transfer Level)記述を自動生成するツールである.論理合成ツールのフロントエンド(前処理)として使用される.現在,市場では米国Forte Design Systems社の「Cynthesizer」と米国Mentor Graphics社の「Catapult」が主に利用されている(日本国内における使用実績という面では,NECの「CyberWorkBench」もよく利用されている).

LSIの設計生産性の危機が叫ばれるようになって以降,何度かビヘイビア合成のブームが到来したが,RTLのEDAツール(論理合成ツールやHDLシミュレータなど)と比べると普及しているとは言い難い状況だ.システムLSI開発やASIC(Application Specific Integrated Circuit)開発,IPコア開発のプロジェクトでは,RTLのVerilog HDLで記述するところから機能設計が始まるケースが多い.

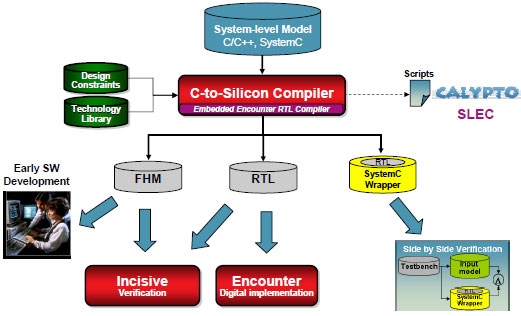

C-to-Silicon Compilerの入力と出力の概要は図1のようになる.入力となるシステム・レベル・モデルの言語はSystemCで,C/C++モデルを入力する場合はSystemCのラッパをを用意する必要がある.このほか,設計制約(回路規模やサイクル数など)とテクノロジ・ライブラリ(.libライブラリ)を入力する.出力となるRTL記述の言語はVerilog HDLである.

[図1] C-to-Silicon Compilerの入力と出力

入力となるシステム・レベル・モデルの言語はSystemC,出力となるRTLモデルの言語はVerilog HDLである.RTLモデル以外に,高速シミュレーション用のモデルやSystemCのラッパなども生成する.

●四つの課題を洗い出し,対策を考える

C-to-Silicon Compilerにつながる同社の取り組みは,2001~2002年ごろに始まったという.Cadence Berkeley Lab(アルゴリズムなどを研究する同社の基礎研究拠点)の研究者が顧客要求の聞き取り調査を行い,その結果,ビヘイビア合成ツールには以下の四つの課題があると結論づけた.

1) データパスと制御論理の混在した設計についての合成結果が悪い

2) 設計修正時にできるだけ小さい範囲だけを合成し直すインクリメンタル合成の機能がない

3) 設計データをリターゲットしたりリユースしたりすることが容易ではない

4) 検証機能のサポートが弱い

1)の課題については,ビヘイビア合成ツールに論理合成ツールを組み込むことで対応した.すなわち,C-to-Silicon Compilerには同社の論理合成ツールであるEncounter RTL Compilerが含まれている.これは,回路規模やサイクル数などの見積もり精度を向上させる目的で組み込んだもので,C-to-Silicon Compilerがゲート・レベル・ネットリストを出力するわけではない.

一般に,ビヘイビア合成ではデータパス部(演算中心の処理で,整然とした回路構成をとる)と制御論理部(ランダムな回路構成をとる)に分けて回路を生成することが多い.データパス部については,スケジューリング(クロックの割り当て)やリソース・シェアリング(演算器やレジスタの共有)といった処理の過程でおおよその回路規模やサイクル数が決まる.一方,制御論理部については実際に論理合成を行ってみないと分からない部分が多い.そこで,論理合成ツールを組み込んで見積もりを行う方式にした.これにより,制御論理の回路規模やサイクル数などを経験的な方法で見積もる場合よりも精度が向上するという.

●ビヘイビア合成の中核は,合成過程を記憶する設計データベース

2)の課題については,新たな設計データベースを一から開発することで対応した.すなわち,合成過程の設計データの変化を効率よく記録・抽出するためのデータベース「Behavior-Structure-Timingデータベース」を開発した.

同社では,このデータベースを中核としてビヘイビア合成ツールを構築している.これにより,入力記述が変更されたとき,合成結果の変更個所ができるだけ少なくなるように,

以前の合成結果を参照しながら再合成できるようになった.

3)の課題については,制約の記述と機能の記述を分離することで対応した.同じ機能でアプリケーションや製造プロセスが異なる製品を開発する場合(例えばH.264のデータ圧縮・伸張機能を携帯型ビデオ・カメラとディジタル・テレビの両方で利用する場合など),入力する設計制約やテクノロジ・ライブラリを差し替えれば両方の回路に対応できる.機能記述に変更を加える必要はなく,設計データの再利用性が向上する.

●実装用モデルに加えて,検証用モデルも生成

4)の課題については,検証用モデルを生成したり,サード・パーティ製ツールとの連携機能を用意することで対応した.

まず,合成したRTLのVerilog HDLモデルをSystemCシミュレーション環境で使えるようにするためのラッパ生成機能を用意した.これは,リファレンス・モデルによる検証(期待値照合)などに利用できる.

さらに,同社がFHM(Fast Hardware Model)と呼ぶ高速シミュレーション用のSystemCモデルを生成する機能も用意した.これは,RTL記述におけるフリップフロップ間の組み合わせ回路を数式や関数に置き換えたモデルである.このモデルを利用すると,アルゴリズム記述(トランザクション・レベルのProgrammer's Viewモデル)を使ってシミュレーションした場合の80~90%程度の速度で論理機能のシミュレーションを実行できるという.

加えて,静的な解析を行う形式的検証ツールとの連携機能も用意した.今回の発表に合わせて,米国Calypto Design Systems社がC-to-Silicon Compilerと連携して動作する形式的検証ツール「SLEC System-HLS(High Level Systhesis)」を発表した(写真2).SLEC Systemは,ビヘイビア合成前のSystemC記述とビヘイビア合成後のRTL記述を比較し,論理的に等価であることをチェックするツールである.順序回路の論理等価性を検証することになるため,状態数が非常に多くなり,一般的な方法では実用的な時間内に解析処理を終えることができない.そこでSLEC Systemでは,最適化の過程で生じる回路のパイプライン段数やレイテンシ,等価ノードなどの情報をビヘイビア合成ツールから受け取り,これを利用して回路を分割・細分化するなどして処理時間を短縮している.今回発表したバージョンでは,パイプライン型の回路構成に対応している.リソース共有型など,そのほかの回路構成についても,今後,順次対応していくという.

[写真2] DA SHOW/CDNLive! Japan 2008の展示エリアの様子

C-to-Silicon CompilerとSLEC System-HLSを組み合わせて使用するデモンストレーションが行われた.左はCalypto社Senior Manager, Field Application Engineeringの山本 修作氏,右はカリプト・デザイン・システムズ 代表取締役社長の鈴木 英機氏.

●顧客の協力を得て製品化へ

Cadence社は約2年前に本ツールを特定顧客(Early Access Customer)へ提供し,問題点を洗い出したり,実設計への適用を開始した.こうした顧客のうちの2社が,今回,同社のプライベート・ショウで導入事例を発表した日立製作所とルネサス テクノロジである.

日立製作所 情報・通信グループ エンタープライズサーバ事業部 開発本部設計技術部の南雲宇晴氏は,「生産性向上を目指した日立のSystemC利用高位設計の取り組み」と題した講演を行った.

同社は,導入の準備段階で,120種類のごく基本的な回路に適用し,人手で作成したRTL記述と同等のものを生成できることを確認した.続いて,受信キューやRAMブロック,アドレス管理,クレジット管理,アービタ制御などから成るスイッチ・コア(ブロック)の方式モデルをビヘイビア合成ツールに入力した.スイッチ・コアのC++モデルにクロックを導入してSystemCモデルとし,これを詳細化してビヘイビア合成を行った.7ファイル,1431行のSystemCモデルが9ファイル,29,000行のRTL記述に変換されたという.さらに,合成時に入力する設計制約のチューニングと仮配置配線を行い,目標とする周波数(400MHz)で動作することを確認した.

現在は,実設計のデータを使ってビヘイビア合成の試行を行っているという.サーバ向けASIC(ノード・コントローラ)のスイッチ部について,ビヘイビア合成ツールの入力となるSystemCモデルを作成した.人手でRTL設計を行った場合と比較して,1/10程度の期間でSystemCモデルを作成できることを確認した.また,RTL設計では数週間かかる仕様レベルの設計変更に,1日(データ・タイプの変更のみ)で対応できたケースもあったという.さらに同社では,社内試作装置などに搭載されているFPGA向けのビヘイビア合成の試行も行っている.

ルネサス テクノロジ 設計技術統括部 システム設計技術開発部の藤井基継氏は,「ルネサス テクノロジにおける高位合成適用事例」と題した講演を行った(写真3).同社では2種類の画像処理IPコアの開発にC-to-Silicon Compilerを適用している.一方の画像処理IPコアについては,人手によるRTL設計と比べて,記述量が約1/3に,シミュレーション時間が約1/6に削減できることを確認した.もう一方の画像処理IPコアについては,論理規模が大きかったため,SystemCモデルを階層化して作成した.また,レイテンシが異なるFPGA向けのRTL記述とシステムLSI向けのRTL記述を同時に作成した.人手による工数の見積もりと比較して,約55%の期間で実現できることを確認した.

同社では,同一機能で要求性能が異なる複数の回路を生成するような用途で,ビヘイビア合成ツール導入の効果が大きいことを実感したという.さらに同社では,ビヘイビア合成前後のSystemC記述とRTL記述の比較を行う形式的検証ツールを利用しているという.

[写真3] ユーザによる導入事例の発表の様子

中央の講演者は,ルネサス テクノロジ 設計技術統括部 システム設計技術開発部の藤井 基継氏.

●高位合成について米国市場に動きあり

ビヘイビア合成ツールについてはこれまで,米国,欧州,日本のうち,日本で最も利用実績が多く,次いで欧州で評価・導入された事例が多いと言われてきた(NEC社内が中心だが,CyberWorkBenchの利用実績が多い).今回のC-to-Silicon Compilerについても,導入事例がまず日本から発信された.一方,米国ではこれまでビヘイビア合成に関する市場の動きは目立たなかったが,ESL(Electronic System Level)設計への注目が高まるにつれて,評価・導入の案件が増えてきているという.

米国,欧州,日本が足並みをそろえてユーザ事例を公表したり,利用ノウハウを蓄積・共有するようになれば,EDA業界は今度こそビヘイビア合成ツール普及への足がかりをつかめるかもしれない.

関連記事

・Mentor,検証用SystemCモデルなどを生成できるC/C++入力のビヘイビア合成ツールを発売

・Bluespec,SystemVerilogライクな記述からRTLのVerilog HDL記述を生成できるビヘイビア合成環境の国内販売を開始

・エッチ・ディー・ラボ,SystemC入力のビヘイビア合成に関する設計ノウハウ集を発売

・技術解説 Cベース設計とは? 導入の課題は?――人手による介入が必須,完全自動合成は幻想

・技術解説 Cベース設計教育の カリキュラム構築から運用まで

・書評百連発 その三十一『C/C++によるVLSI設計――SystemCによるJPEGコーデック設計』