LSIレイアウト設計関連で新機軸を盛り込んだツールが続々 ――分散処理/ルール・ドリブン・レイアウト,LC考慮のIRドロップ解析

米国カリフォルニア州Anaheimで2003年6月2日~6日に開催された40th Design Automation Conference(40th DAC)では,LSIのレイアウト設計関連のツールが来場者の注目を集めていた.90nmプロセスのLSIの量産化を目前にひかえ,大規模な回路に対応するための新しいアイデアを盛り込んだレイアウト・ツールや解析ツールが続々登場している.

●分散処理に対応したシェイプ・ベースのレイアウト・ツールが登場

英国Pulsic社は,大規模なセル・ベースLSI向けのレイアウト・ツール「Prelude Physical Design Framework」を発表した(写真1).これまで同社は,主にフルカスタムLSIやメモリLSI向けのレイアウト・ツール(Lyric)を出荷していた.今回,複数のコンピュータの上で自動配置配線の分散処理を行えるように改良し,数百万のネットと数百万のセルを含むレイアウト・データを処理できるようになったという.LSFなどのワークロード管理ソフトウェアにも対応している.

[写真1] Prelude Physical Design Frameworkのデモンストレーションが行われたPulsicのブース

同社の自動配置配線ツールはシェイプ・ベース方式(グリッドレス方式)を採用している.この方式は,あらかじめ指定された間隔の格子の上にセルや配線を乗せていくグリッド方式と異なり,セルや配線の位置の微調整を行いやすいという利点がある.また,ECO(engineering change order)などにも対応しやすい.ただし,データ量が多くなり,処理の負荷が重くなるという欠点があった.同社では,こうした問題を分散処理とデータベース技術のくふうによって解消したという.また,本ツールは45度配線(斜め配線)にも対応できるという.

同社は今回の製品を,主にECO用途のレイアウト最適化ツールとして出荷していく方針.米国Cadence Design Systems社や米国Synopsys社のツールを利用して配置配線を行った後,レイアウト・データを受け取って本ツールによって最適化処理を施す.

なお,同社のフルカスタムLSIやメモリLSI向けのレイアウト・ツールは,レイアウト設計環境を出荷してるセイコーインスツルメンツにOEM供給されている.また,エルピーダ・メモリが0.11μmルールの設計環境に採用しているという.

●サード・パーティのレイアウト・ツールを分散処理対応に

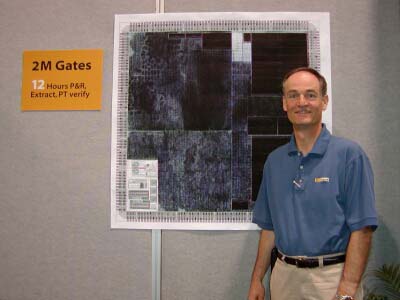

米国ReShape社は,サード・パーティの自動配置配線ツールや各種解析ツールを利用しながらレイアウト設計の分散処理を実現するツール「GDS Builder」を発表した(写真2).本ツールは,フロアプランナ,サード・パーティのツールを管理・制御する機能,レイアウト・データベース,レイアウト情報のフォーマット変換ツールなどからなる.いわゆるレイアウト設計ツール(自動配置配線ツール,レイアウト検証ツール,レイアウト・エディタなど)や解析ツールは含んでいない.

[写真2] GDS Builderを使用して設計されたチップのレイアウト(右側は同社Vice President of Business DevelopmentのBob Dahlberg氏)

本ツールでは,フロアプランナを利用してネットリストを適当なサイズ(25万インスタンス程度)に分割し,タイミング・バジェッティング(境界をまたぐパスに対するタイミングの割り付け)を行った後,サード・パーティのツールを使って各ブロックの配置配線や各種解析を実行する.このとき,複数のコンピュータを利用してブロック単位に分散処理を行う.例えば,ブロックの境界のピン配置が不適当であれば,ピン配置を変更して繰り返し配置配線を行う.また,ブロックをまたぐグローバル配線のタイミングに問題があれば,自動的にリピータを挿入する.

本ツールに組み込んで利用できるサード・パーティのツールは,Cadence社のCeltic,Synopsys社のAstro,Apollo,Formality,Hercules,Mars Rail,Astro Rail,PrimeTime,Star-RCXT,米国Mentor Graphics社のCalibreである.2003年第3四半期には,Cadence社のFire & Ice QXC,First Encounter,NanoRoute,PKS Encounter,Virtuoso,Voltage Storm SOC,Warp Routeにも対応する予定.

●設計ルールで制御しながらフルカスタムLSIを自動レイアウト

米国Silicon Canvas社は,同社のフルカスタムLSI向け自動レイアウト・ツールの新バージョン「Laker 3.1」を発表した.設計ルールを入力すると,それに合わせてセル・ジェネレータ「Magic Cell」がセルのレイアウトを生成する.また,自動配線の際にも,設計ルールを制約として与えることができる.これまで,フルカスタムLSIのレイアウト設計にはP-cell(パラメタライズド・セル)が利用されてきた.P-cellを利用する場合,セルの幾何的な情報をプログラムとして与える必要がある.本ツールでは,こうしたプログラムを作成する必要がないという.

ユーザはSPICEネットリストを入力する.出力はGDS IIのマスク・レイアウトである.本ツールは,セル・ジェネレータ,シェイプ・ベース方式の自動配線ツールのほか,レイアウト・データから回路図を抽出するツール,セルのテンプレート,DRC(design rule checker),LVS(layout versus schematic),ERC(electrical rule checker),ソース・ブラウザ,セル・レイアウトのシンボリック表示/編集ツール(Stick Diagram)などを備えている.また,Cadence社のデータベース「Open Access」,Synopsys社のデータベース「Milkyway」との間のインターフェース・ソフトウェアを用意している.

2004年に出荷を予定している次期バージョンの「Laker 4.x」では,アプリケーションに合わせた最適化機能を用意していく方針.例えば,メモリ向けのレイアウト・ツールでは,メモリ・ブロックのアスペクト比を制御できるようにするという.

●電源ラインのLCやパッケージの影響まで考慮してIRドロップ解析

米国Apache Design Solutions社は,大規模LSIの電源ラインのIRドロップ(電圧降下)を計算する消費電力解析ツール「RedHawk-SDL」のデモンストレーションを行った.従来のIRドロップの解析では,電源ラインの電流値を時間的に一定とみなして計算する(つまり電流の平均値を利用する)場合が多かった.本ツールでは,過渡解析を行って電流値の変動を計算している.すなわち,R(抵抗)だけでなく,電流に対するL(インダクタンス)やC(キャパシタンス)の影響まで含めて,IRドロップを解析している.そのため,解析の精度が高いという.さらに,外部に付加されるパッケージの抵抗成分やインダクタンス成分,デカップリング・キャパシタなども含めて解析することができる.

また,本ツールでは,入力パターンを与えながら全体の機能動作を模擬するダイナミックなシミュレーションは行っていない.制約付きの統計値によって,論理ゲートのスイッチング情報(スイッチング・シナリオ)を与えている.例えば,数百万ゲートのLSIを解析する場合,ワースト・ケースの状況を再現する入力パターンを用意することは,事実上不可能である.本ツールでは,ダイナミック・シミュレーションを行っていないため,処理時間が大幅に短縮する.例えば,300MHz~600MHzのクロックで動作する400万ゲートのLSIに適用したところ,2時間程度で解析が終了したという(一般に,電源ラインの消費電力解析には1日程度かかる場合が多い).

本ツールの入力は,LEF/DEF,GDS IIのマスク・データ,および.libライブラリである.また,レイアウト情報から寄生容量や寄生抵抗を抽出した後のSPICEネットリスト,静的タイミング解析ツールで計算した遅延情報も入力として利用できる.

●グラフィカル表現を利用してプロパティ言語PSLを入力

次に,RTL(register transfer level)以上を対象とした設計ツール(フロントエンド・ツール)の発表を紹介する.

英国TransEDA社は,プロパティ言語PSL(Property Specification Language;Accelleraが標準として採用したプロパティ言語で,IBM社が開発した言語Sugerがベースとなっている)を生成するグラフィカル入力/編集ツール「PA-Studio」を発表した(写真3).プロパティ言語は時間の概念を含む論理(時相論理)を表現するための言語であり,習熟に時間がかかると言われている.本ツールを使えば,プロパティ言語の体系やPSLの構文に慣れていない設計者でも,エラーのないPSL記述を作成できるという.また,VCD(value change dump)ファイルを読み込み,シミュレーション・パターンを利用して,本プロパティにエラーがないかどうかを確認することができる.さらに,波形入力/編集機能も備えている.

[写真3] PA-Studioのデモンストレーションが行われたTransEDA社のブース

本ツールは,TransEDA社のプロパティ検証ツール(VN-PropertyDX)だけでなく,PSLに対応する他社のプロパティ検証ツールと組み合わせて利用することもできる.

●国産C入力ビヘイビア合成ツールが並行処理記述をサポート

数少ない国産EDAツールのベンダであるフューチャーデザインオートメーションは,DACの会場でシステム・レベル設計環境「SystemCenter」のデモンストレーションを行った(写真4).SystemCenterには,ビヘイビア合成ツール「DesignPrototyper」,回路ライブラリ,RTL記述を編集できるHDLエディタが含まれている.入力言語はSystemCまたはANSI C.

また,同社のビヘイビア合成ツールが並行処理のための構文(par構文)をサポートしたことも明らかにした.この構文を利用して並行処理を行うモジュールを明示的に記述すると,処理速度の速い回路が生成されるという.

[写真4] SystemCenterのデモンストレーションが行われたフューチャーデザインオートメーションのブース(中央は,同社開発部の肥田野正輝氏)