カスタム命令を備える特定用途向けプロセッサ関連の製品が続々登場 ――EDS(Electronic Design and Solution) Fair 2003

2003年1月30日(木)~31日(金),パシフィコ横浜(神奈川県横浜市)にて,LSI設計技術関連の展示会「EDS(Electronic Design and Solution) Fair 2003」が開催された(写真1).今回のEDS Fairでは,カスタム命令などを備える特定用途向けプロセッサの開発に焦点を合わせた製品の展示が目立っていた.また,本展示会に合わせて,SystemCやSystemVerilogといったシステム・レベル言語に関するロードマップの発表も行われた.

〔写真1〕EDS Fair 2003の会場風景

神奈川県横浜市のパシフィコ横浜で開催された.

●カスタム・プロセッサとソフト開発環境を自動生成

従来,「特定用途向けプロセッサ」というと,CPUコアにさまざまな周辺回路を付加した組み込み用マイクロコントローラや,積和演算機能を強化したディジタル信号処理プロセッサ(DSP)などを思い浮かべることが多かった.しかし最近では,メディア・プロセッサ(画像/音声処理向けプロセッサ)やネットワーク・プロセッサ,I/Oプロセッサなど,用途を絞ったプロセッサが多数登場している.また,機器メーカがCPUコアを内蔵するASIC(主に機器メーカが開発する特定用途向けLSI)やコンフィギャラブル・プロセッサ(米国Tensilica社のXtensa,米国ARC International社のARCtangentなど)を開発する例も増えている.

こうした動きを受けて,カスタム命令を備える特定用途向けプロセッサの開発に焦点をあてた設計支援用の製品が続々登場している.本展示会でも,独自の命令セット・アーキテクチャを持つプロセッサを開発できる設計環境,コンフィギャラブル・プロセッサのIPコア,Cコンパイラの開発環境など,カスタム・プロセッサ関連の展示や発表が相次いだ.

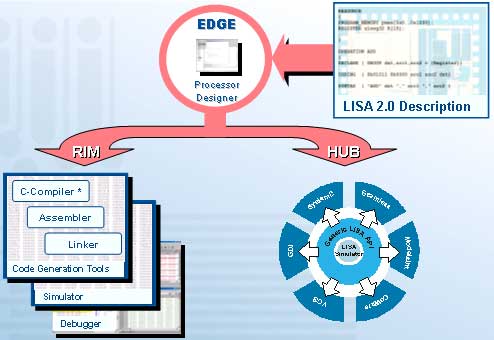

まず,ハードウェア・ソフトウェア協調設計/検証ツールを提供している米国CoWare社が,カスタム・プロセッサ開発ツールを出荷しているドイツLISATek社の買収を発表した.LISA Tek社のツールは,命令セット・アーキテクチャを定義したファイルから,機能検証やハードウェア・ソフトウェア協調検証に必要なシミュレーション・モデル(Verilog HDL,VHDL,SystemC,CoWare Cなど),CPUコアのRTL(register transfer level)データ,ソフトウェア開発ツール(Cコンパイラ,アセンブラ,リンカ,命令セット・シミュレータ,デバッガなど)などを自動生成する(図1).命令セット・アーキテクチャの定義には「LISA(Language for Instruction Set Architecture)」と呼ばれる言語を利用する.

なおCoWare社によると,Tensilica社やARC International 社と異なり,本ツールで開発したカスタム・プロセッサをIPコアの形態で顧客に提供する予定はないという.「当社はあくまでも設計支援ツールとして販売する方針.IPコア製品として提供している企業の多くは,チップに対するロイヤリティの徴収で収益を上げている.基本的に,LISA Tek社のツールがこうしたベンダの製品と競合することはないと考えている」(CoWare社).

〔図1〕LISATek社の製品

LISA言語を使って命令セット・アーキテクチャを定義する.EDGEと呼ぶツールでプロセッサを設計し,HUBを使ってシミュレーション・モデルを生成する.また,RIMと呼ぶツールを使うと,ソフトウェア開発環境が自動生成される.

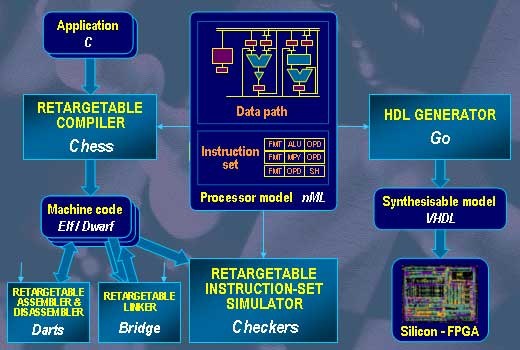

また,ベルギーTarget Compiler Technologies社は,特定用途向けディジタル信号処理プロセッサ(DSP)開発ツール「CHESS/CHECKERS」のデモンストレーションを行った.ユーザは,nMLと呼ぶ言語を使ってデータパス回路と命令セット・アーキテクチャを定義する.同社のツールは,この定義ファイル(プロセッサ・モデル)からRTLのVHDLデータ,命令セット・シミュレータ,Cコンパイラ,リンカなどを自動生成する(図2).

〔図2〕Target社の製品

特定用途向けのディジタル信号処理プロセッサとその開発環境を自動生成する.

●ユーザ定義命令を追加できる32ビットCPUコアが続々

一方,コンフィギャラブル・プロセッサ「VUPU」を提供しているパシフィック・デザインは,32ビットRISCプロセッサ・コア「PU/P4」を新たに発表した.同社はこれまで,VUPU向けに16ビットのRISCプロセッサ・コアを提供していた.

PU/P4は32ビット汎用レジスタを16個内蔵する.パイプラインは,1) 命令フェッチ,2) デコード,3) 実行,4) メモリ/ライト・バックの4段構成.命令数は236.これにユーザ定義命令を処理する回路(ハード・ワイヤード論理)「VU」を接続して,コンフィギャラブル・プロセッサを実現する.VUPU用のCコンパイラの生成には,オランダACE(Associated Compiler Experts)社のコンパイラ開発ツール「CoSy」を利用している.PU/P4は2003年第1四半期に出荷する予定.また,同社はVUの演算器ライブラリやサブルーチン・ライブラリも提供する.乗算器や除算器,積和演算器,FFT(高速フーリエ変換),IDCT(逆離散コサイン変換)などのマクロを用意する.

今回のEDS Fairには出展していないが,米国MIPS Technologies社もユーザ定義命令を追加できるプロセッサ・コア「Pro Series」を発表している.32ビットRISCコアである4KSd,M4K,4KEp,4KEm,4KEcにユーザ定義命令を追加できるようになった.ユーザに16個のOPコードを開放した.ユーザ定義命令を処理する回路(CorExtendブロック)はRTLのVerilog HDLコードで記述する.本プロセッサ・コアのソフトウェア開発環境として,同社の「MIPSsde 5.0」と米国Green Hills Software社の「MULTI」が対応している.

このほか,本展示会では,東芝がコンフィギャラブル・プロセッサ「MeP(Media embedded Processor)」について,ARC International社の国内販売代理店であるアイヴィスが「ARCtangent」などについて,ACE社の国内販売代理店である日本ノーベルがACE社のCコンパイラ開発ツール「CoSy」についてパネル展示などを行った.これまでカスタム・プロセッサを設計するのは半導体メーカに所属するプロセッサ開発のエキスパートに限られていた.しかし,今後は,機器メーカのASIC設計者なども比較的容易にカスタム・プロセッサやソフトウェア・ツールなどを開発できる状況になりそうだ.

●SystemCが2003年度中にIEEEへ標準化申請

システム・レベル言語SystemCの標準化・普及推進団体である米国OSCI(Open SystemC Initiative)は,2003年4月にSystemCのLRM(言語リファレンス・マニュアル)を公開すること,およびこのLRMをもとに2003年度中に米国IEEE(The Institute of Electrical and Electronics Engineers, Inc.)へ標準化申請を行うことを発表した.本展示会の会期中に開催された「第3回日本SystemCユーザフォーラム(写真2)」で,同団体のVice-Chaimanである長谷川隆氏が明らかにした.

また,OSCIは,2003年4月にSystemC 2.1とSystemC Verification Standard 1.0の正式版を公開する(現在はβ版を提供中).SystemC 2.1には,動的スレッドのしくみや並列処理のためのfolk/joinの記述が新たに追加されている.SystemC Verification Standardは,検証用のC++クラス・ライブラリである.

このほか,OSCIでは組み込みソフトウェアやリアルタイムOSのモデル化に対応したSystemC 3.0を開発中.現在,要求仕様書が完成しており,そのレビューを行っているという.また,2002年10月にはSysnthesis Working Groupを設置しており,ビヘイビア・レベルとRTLの合成用記述の仕様(合成サブセット)とその記述ガイドラインの策定なども始めている.

SystemCについては,国内企業の間で動きが出てきたことも最近の特徴である.まず,日立インフォメーションテクノロジとエッチ・ディー・ラボがSystemCに関する教育サービスを開始した.また,組み込みソフトウェア開発ツールを発売しているキャッツは,UML(Unified Modeling Language)記述をSystemC記述に変換するツール「XModelink」を昨年(2002年)11月に発表している.さらに,ビヘイビア合成ツール「Design Prototyper」を開発しているフューチャーデザインオートメーションや,SpecC向けの仕様設計ツール「VisualSpec」を開発しているインターデザインテクノロジーがSystemCのサポートを表明している.

〔写真2〕第3回日本SystemCユーザフォーラムの風景

STマイクロエレクトロニクス デジタルコンスーマーグループ 技術開発センター DTV&Imagingプロジェクト 課長の生駒朗氏による講演のようす.このほか,三洋電機,松下電器産業,エッチ・ディー・ラボがユーザの立場で講演した.

●AccelleraがSystemVerilogとプロパティ言語の文法を共通化

ハードウェア記述言語やEDA関連の標準化団体である米国Accelleraは,システム・レベル言語「SystemVerilog」のアサーション記述とプロパティ言語「PSL(Property Specication Language)」の文法を共通化していくことを発表した.「100%のセマンティクスと97%のシンタックスが共通になるだろう」(Accellera,ChairmanのDennis B. Brophy氏,写真3).SystemVerilogは現行のVerilog HDLをシステム・レベル設計向けに拡張した言語である.C言語と同様の構文を含んでおり,テストベンチやシステム・レベル・モデルを作成しやすいという特徴がある.一方,PSLはフォーマル・ベリフィケーション(形式的検証)の一種であるプロパティ検証専用の記述言語である.米国IBM社が開発した言語「Sugar」をベースとしている.どちらの言語もAccelleraが標準化を進めている.

Accelleraによると,2003年3~4月ごろ公開される「PSL 1.1」,および2003年5月ごろ最終ドラフトがまとまる予定の「SystemVerilog 3.1」によって,上述の共通化が実現するという.

SystemVerilogについては,すでにいくつかのEDAベンダが対応を表明している.米国Mentor Graphics社は2003年内に合成,シミュレーション,ハードウェア・ソフトウェア協調検証,エミュレーションなどのツールをSystemVerilogに対応させていくという.一方,米国Synopsys社は,Verilog HDLシミュレータ「VCS」のSystemVerilog 3.0対応版を2003年3月ごろ,SystemVerilog 3.1対応版を2003年末に発表すると表明.さらに,論理合成ツール「Design Compiler」や「Module Compiler」もSystemVerilogに対応させていくという.同社は2002年9月に,SystemVerilogのたたき台となった言語「Superlog」とそのシミュレーション環境を開発した米国Co-Design Automation社を買収している.

〔写真3〕Accelleraがアサーション関連のロードマップを発表

右側がAccellera, ChairmanのDennis B. Brophy氏.左側はSynopsys社 Senior Director of Marketing, Verification Technology GroupのDave Kelf氏.