カスタム命令を備える特定用途向けプロセッサ関連の製品が続々登場 ――EDS(Electronic Design and Solution) Fair 2003

●プロトコル処理用の回路やスタック・ソフトウェアを生成

NTTアドバンステクノロジのブースでは,米国Novilit社の通信プロトコル開発ツール「AnyWare 2.0」が展示されていた(写真4).NTTアドバンステクノロジは2003年1月にNovilit社と販売代理店契約を結んだ.

AnyWareは,任意のプロトコル処理回路やプロトコル・スタック・ソフトウェアを開発するためのツールである.ユーザは「CMDL」と呼ぶ専用言語で通信プロトコルの仕様を記述する.AnyWareは,この記述からC/C++,Java,およびRTLのVHDLやVerilog HDLのコードを生成する.所望のプロトコルに従っているかどうかをチェックするためのデバッグ環境も用意する.

IPv4やIPv6,MPEG-2,TCPなど,50種類以上の規格のプロトコル処理やデコード処理に対応している.暗号処理などは,別途C++などでプログラミングして取り込む必要がある.

〔写真4〕AnyWareのデモンストレーション

デモンストレーション用に作成された通信プロトコル(TAILプロトコル)をCMDLで記述した.画面上の[VHDL]ボタンや[C++]ボタンを押して,コードを生成する.

●3,000万ゲート対応の論理エミュレータが登場

メンター・グラフィックス・ジャパン(Mentor Graphics社の日本法人)は,論理エミュレータ「CelaroPRO」を展示した(写真5).CelaroPROは同社の「Celaro」の後継にあたり,最大3,000万ゲートの論理回路を実現できる.これは従来のCelaroの2~4倍の回路規模.Celaro同様,FPGAではなく,専用のカスタム・チップを多数使用して,大規模な論理回路を構成する.論理エミュレータには市販のFPGAを利用して論理回路を構成する方式もある.Celaroのようにカスタム・チップを利用すると,前処理のコンパイル(FPGAを使用する場合は配置配線処理など)にかかる時間が短くなるという利点がある.なお,同社は米国Xilinx社のFPGAを利用する論理エミュレータ「VStation(旧IKOS Systems社の製品)」も出荷している.

CelaroPROは,同社のHDLシミュレータ「ModelSim」やハードウェア/ソフトウェア協調検証ツール「SeamlessCVE」,米国Cadence Design Systems社の論理シミュレータ「NC-Sim」,米国Verisity Design社のテストベンチ設計環境「Specman Elite」などと組み合わせて利用することもできる.

〔写真5〕3,000万ゲートの回路を検証できる論理エミュレータ

論理エミュレータ「CelaroPRO」の外観.筐体の上段と下段にそれぞれ24のスロットを持つ.カスタム・プロセッサを搭載したロジック・ボード(ボード2枚で1組)を最大24組挿入することができる.

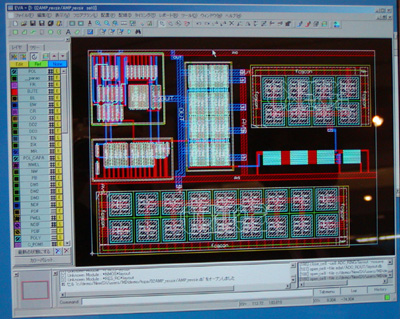

●過去のアナログ・レイアウト情報から配置制約を自動抽出

セイコーインスツルメンツは,アナログ/ミックスト・シグナルIC向けの自動配置ツール「AMPER」を展示した(写真6).AMPERは,既存のレイアウト・データから配置制約を抽出する機能を備えている.例えば,「どの素子とどの素子を隣接させるか」,「どの素子とどの素子を遠ざけるか」,「どの素子を電源やグラウンドの隣に置くか」といったルールを自動的に抽出する.また,回路図上の回路図シンボルの相対配置をレイアウト上の素子の配置に反映させる機能も備えている.これはバイポーラICの設計などで有効な機能である.このほか,素子の対称配置やアライン配置(列状に並べる配置),グループ化などの制約を人手で指定することができる.

自動配置ツールは,ネットリストと配置制約情報を基に,チップ上の素子の最適配置を計算するソフトウェアである.チップ面積を小さくするため,素子の位置を入れ替えたり,同電位の端子をマージする機能を備えている(いわゆるコンパクション).

本自動配置ツールは,素子の数が数百程度のICの配置に利用できる.100素子程度の回路の配置に30~40分かかるという.同社のレイアウト設計環境「SX-9000」や「New-SX」に組み込んで利用する.同社が現在開発している配線ツール「REXSIR」と組み合わせると,アナログICの配置と配線を一括して行うことができるという.AMPERの出荷開始時期は2003年4月の予定.

〔写真6〕既存のレイアウト・データから配置制約を抽出する機能を備える自動配置ツール

セイコーインスツルメンツの「AMPER」.回路図上の回路図シンボルの配置をレイアウトに反映させることもできる.

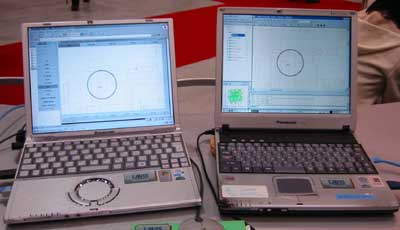

●複数の拠点の設計者が同時に閲覧できるレイアウト・ビューワ

TOOLは,複数の拠点の設計者が一つのレイアウト・データを同時に閲覧できるLSIレイアウト・ビューワ「LAVIS 2.5」のデモンストレーションを行った(写真7).レイアウト図面上に図形を描いたり,文字を書き込む機能を備えている.拠点間のデータのやりとりにはインターネットを利用する.また,Mentor Graphics社のレイアウト検証ツール「Calibre RVE」が検出したエラー箇所を表示する機能も備えている.

〔写真7〕LAVIS 2.0のリモート・ビューワ機能

LAVIS本体(写真右)で表示範囲を指定する.ユーザ名とパスワードを入力すると,クライアント(写真左)側でも同じレイアウト情報を閲覧できる.また,クライアント側で表示範囲を指定したり,移動させることも可能である.