ARMプロセッサを開発する際にフィジカルIPで効率的に最適化するテクニック

ここでは,ARM社のフィジカルIP(レイアウト・レベルの回路ライブラリ)である「Processor Optimization Package(POP)」について,その主要な構成,シリコン・チップ化したときのベンチマーク結果,および実装上のテクニックを紹介します.POPはARMプロセッサを効率よく,また性能と消費電力をバランスよく最適化できるライブラリです.

●プロセッサ開発の期間を短縮し,リスクを低減

Cortex-Aファミリのプロセッサは,セットトップ・ボックスやモバイル機器,インターネット接続機器などのアプリケーションにおいて広く使われており,市場拡大をけん引する役割を果たしました.

多くのアプリケーションはマルチプロセッシング機能だけでなく,シングル・スレッドの実行時にも高い性能を要求します.Cortex-A9 Processor Optimization Package(POP)を利用してチップを開発すれば,マルチスレッドやマルチコアのプロセッサにおいても高速動作とARMプロセッサの特徴である低消費電力を両立できます.ARM Artisan POPを利用することで,ARMプロセッサを設計・製造する半導体メーカは,製品の市場投入にかかる期間(Time to Market)を短縮できます.また,開発時のリスクを低減でき,かつレイアウト設計工程の作業を円滑に進められるようになります.

●最先端プロセスのライブラリ開発をけん引

ARM社はPOPのファミリ展開を行っています.これらのパッケージを利用すると,Cortex-Aプロセッサのレイアウト設計において,半導体メーカは競争力のあるPPA(Power, Performance and Area)を実現できます.

提供するフィジカルIPには,特定セルを最適化したもの,およびCortex-A9プロセッサのクリティカル・パスを最適化するセルなどが含まれています.ARM社は,POPの提供を通して,TSMC 40nm,Samsung 32nm/28nm,TSMC 28nmなどの最先端プロセスの立ち上げにおいて,ライブラリ開発のけん引役となっています.ARM社は,POPのフィジカルIPのほか,レイアウトした際のベンチマーク結果や技術サポート(技術知識の移転)も提供しています.

●高速SRAM,高速標準セル,HPK,PMKから構成

POPのフィジカルIPには,マルチコア構成のCortex-A9 MPCoreに最適化された高速SRAM(FCI:Fast Cache Instances),高速スタンダード・セル(12トラックの高性能版),HPK(High Performance Kit),PMK(Power Management Kit)が含まれます.これらのライブラリは多電源に対応しており,リーク電流と消費電力を最適化するための電源分離などをサポートしています.

マルチチャネル,マルチVtスタンダード・セルは,異なるしきい値電圧のトランジスタといくつかのゲート幅のライブラリから構成されます.マルチチャネル・ライブラリを利用すると,レイアウト設計において,リーク電流の最適化,および性能と消費電力のトレードオフ評価が容易に行えます.

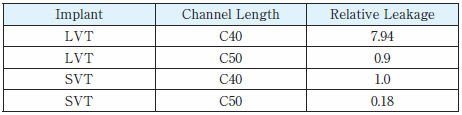

表1に,TSMC 40nm LP(ローパワー)プロセスにおけるマルチチャネル,マルチVtトランジスタのリーク電流を示します.これらのトランジスタを組み合わせることにより,プロセッサのレイアウト設計において,最大限の低電力化を実現できます.

表1 CLN40LPのリーク電流

すべての基本セル,PMK,HPKは,一つのブロックや一つのデザインにおいて,同じロー(ROW)に共存する形で使用できます.スタンダード・セルについては,特別な境界を設定したり,複雑な構造を作り込む必要はありません.またECOキットも,これらのセルと共存して使用できます.ECOセルは,あらかじめ配置されたFillerセルを用い,マスク・レイヤを変更することで,異なる機能のセルを実現できます.つまり,容易に論理を変更できます.

FCI専用の高速キャッシュSRAMはCortex-A9専用に特別にカスタマイズされたもので,セットアップ時間とアクセス時間のバランスが絶妙に調整されています.ARM社はプロセッサの設計において,クロック周波数を決める際に高速キャッシュSRAMが性能向上のボトルネックとならないように,セットアップ時間とアクセス時間を慎重に,そしてプロセスごとに最適化しています.

●すべてのベンチマークに最悪条件を採用

実際のチップの設計では,プロセスの最悪条件に対応したマージンを持たせ,製造工程で生じるバラツキに配慮します.バラツキの要因は,プロセス,電源電圧,温度条件などに分類されます.

プロセスに関するバラツキは,トランジスタやメタルの膜厚のバラツキに起因するもので,トランジスタの性能に影響を及ぼします.電源電圧に関するバラツキは電源降下によるものですが,その要因は,電源電圧そのものの電圧降下と,SoC(System on a Chip)の設計に起因するトランジスタ素子の電圧降下に分かれます.温度に関するバラツキはチップの動作環境に依存し,高温と低温でデバイス特性が異なります.

ARM社は,すべてのベンチマーク評価において最悪条件を採用しています.悲観的な設計マージンを適用し,信頼できるベンチマーク結果を提供しています.ARMプロセッサを設計・製造する半導体メーカにおいても,最悪条件のベンチマーク結果を再現でき,マージンの設定しだいではさらなる最適化も行えます.そして,最終製品に求められる性能を迅速に実現できます.

それぞれのベンチマーク結果をもとに,POPのフィジカルIPを利用する設計フローが改善されます.ARM社は,Cortex-Aプロセッサとそのレイアウト設計に必要なフィジカルIPについて,最適な回路を実現できる知識と経験をもっています.

コア構成のベンチマークでは,デュアルコアとシングル・コアのそれぞれについて性能を比較し,コア構成ごとの性能を厳密に評価します.ARM社は市場の動向を理解しており,デュアルコアのCortex-A9が幾つかのアプリケーションにおいて最適なシステム構成であることを理解しています.これは二つのL1プロセッサと一つのL2コントローラで構成され,それらはL1サブシステムと同等のクロック周波数で動作するように設計されます.L2コントローラへ分配されるCPUクロックについては,L1からL2へのクロック・レイテンシを最適化することがもっとも重要となります.POPの開発は,L1/L2サブシステム全体のベンチマーク評価に必要不可欠な存在と位置付けられています.

●POPを利用すると性能が28%改善

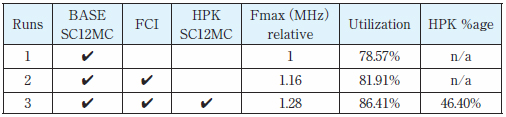

表2にベンチマーク結果の例を示します.POPのFCIやHPKの効果が一目瞭然で理解できます.このベンチマークではContex-A9のサブブロックの結果が示されており,POPを利用することで28%もの性能改善が確認できます.

表2 CLN40LP POPのベンチマーク例

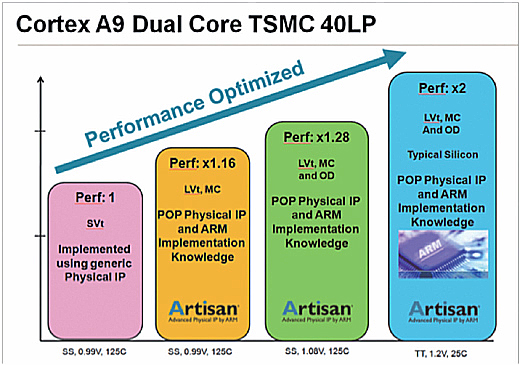

図1に,TSMC 40nm LPプロセスにおける性能のベンチマーク結果を示します.

図1 TSMC 40nm LPの性能

さとう・ひろあき

アーム(株) ARM physical IP Strategic Accounts Merketing